|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Data Structures | |

| struct | tDMAControlTable |

Macros | |

| #define | uDMATaskStructEntry(ui32TransferCount, ui32ItemSize, ui32SrcIncrement, pvSrcAddr, ui32DstIncrement, pvDstAddr, ui32ArbSize, ui32Mode) |

Functions | |

| void | uDMAEnable (void) |

| void | uDMADisable (void) |

| uint32_t | uDMAErrorStatusGet (void) |

| void | uDMAErrorStatusClear (void) |

| void | uDMAChannelEnable (uint32_t ui32ChannelNum) |

| void | uDMAChannelDisable (uint32_t ui32ChannelNum) |

| bool | uDMAChannelIsEnabled (uint32_t ui32ChannelNum) |

| void | uDMAControlBaseSet (void *psControlTable) |

| void * | uDMAControlBaseGet (void) |

| void * | uDMAControlAlternateBaseGet (void) |

| void | uDMAChannelRequest (uint32_t ui32ChannelNum) |

| void | uDMAChannelAttributeEnable (uint32_t ui32ChannelNum, uint32_t ui32Attr) |

| void | uDMAChannelAttributeDisable (uint32_t ui32ChannelNum, uint32_t ui32Attr) |

| uint32_t | uDMAChannelAttributeGet (uint32_t ui32ChannelNum) |

| void | uDMAChannelControlSet (uint32_t ui32ChannelStructIndex, uint32_t ui32Control) |

| void | uDMAChannelTransferSet (uint32_t ui32ChannelStructIndex, uint32_t ui32Mode, void *pvSrcAddr, void *pvDstAddr, uint32_t ui32TransferSize) |

| void | uDMAChannelScatterGatherSet (uint32_t ui32ChannelNum, uint32_t ui32TaskCount, void *pvTaskList, uint32_t ui32IsPeriphSG) |

| uint32_t | uDMAChannelSizeGet (uint32_t ui32ChannelStructIndex) |

| uint32_t | uDMAChannelModeGet (uint32_t ui32ChannelStructIndex) |

| void | uDMAIntRegister (uint32_t ui32IntChannel, void(*pfnHandler)(void)) |

| void | uDMAIntUnregister (uint32_t ui32IntChannel) |

| uint32_t | uDMAIntStatus (void) |

| void | uDMAIntClear (uint32_t ui32ChanMask) |

| void | uDMAChannelAssign (uint32_t ui32Mapping) |

| void | uDMAChannelSelectSecondary (uint32_t ui32SecPeriphs) |

| void | uDMAChannelSelectDefault (uint32_t ui32DefPeriphs) |

| #define uDMATaskStructEntry | ( | ui32TransferCount, | |

| ui32ItemSize, | |||

| ui32SrcIncrement, | |||

| pvSrcAddr, | |||

| ui32DstIncrement, | |||

| pvDstAddr, | |||

| ui32ArbSize, | |||

| ui32Mode | |||

| ) |

A helper macro for building scatter-gather task table entries.

| ui32TransferCount | is the count of items to transfer for this task. |

| ui32ItemSize | is the bit size of the items to transfer for this task. |

| ui32SrcIncrement | is the bit size increment for source data. |

| pvSrcAddr | is the starting address of the data to transfer. |

| ui32DstIncrement | is the bit size increment for destination data. |

| pvDstAddr | is the starting address of the destination data. |

| ui32ArbSize | is the arbitration size to use for the transfer task. |

| ui32Mode | is the transfer mode for this task. |

This macro is intended to be used to help populate a table of uDMA tasks for a scatter-gather transfer. This macro will calculate the values for the fields of a task structure entry based on the input parameters.

There are specific requirements for the values of each parameter. No checking is done so it is up to the caller to ensure that correct values are used for the parameters.

The ui32TransferCount parameter is the number of items that will be transferred by this task. It must be in the range 1-1024.

The ui32ItemSize parameter is the bit size of the transfer data. It must be one of UDMA_SIZE_8, UDMA_SIZE_16, or UDMA_SIZE_32.

The ui32SrcIncrement parameter is the increment size for the source data. It must be one of UDMA_SRC_INC_8, UDMA_SRC_INC_16, UDMA_SRC_INC_32, or UDMA_SRC_INC_NONE.

The pvSrcAddr parameter is a void pointer to the beginning of the source data.

The ui32DstIncrement parameter is the increment size for the destination data. It must be one of UDMA_DST_INC_8, UDMA_DST_INC_16, UDMA_DST_INC_32, or UDMA_DST_INC_NONE.

The pvDstAddr parameter is a void pointer to the beginning of the location where the data will be transferred.

The ui32ArbSize parameter is the arbitration size for the transfer, and must be one of UDMA_ARB_1, UDMA_ARB_2, UDMA_ARB_4, and so on up to UDMA_ARB_1024. This is used to select the arbitration size in powers of 2, from 1 to 1024.

The ui32Mode parameter is the mode to use for this transfer task. It must be one of UDMA_MODE_BASIC, UDMA_MODE_AUTO, UDMA_MODE_MEM_SCATTER_GATHER, or UDMA_MODE_PER_SCATTER_GATHER. Note that normally all tasks will be one of the scatter-gather modes while the last task is a task list will be AUTO or BASIC.

This macro is intended to be used to initialize individual entries of a structure of tDMAControlTable type, like this:

//! tDMAControlTable MyTaskList[] =

//! {

//! uDMATaskStructEntry(Task1Count, UDMA_SIZE_8,

//! UDMA_SRC_INC_8, MySourceBuf,

//! UDMA_DST_INC_8, MyDestBuf,

//! UDMA_ARB_8, UDMA_MODE_MEM_SCATTER_GATHER),

//! uDMATaskStructEntry(Task2Count, ...),

//! }

//! \return Nothing; this is not a function.

| void uDMAChannelAssign | ( | uint32_t | ui32Mapping | ) |

Assigns a peripheral mapping for a uDMA channel.

| ui32Mapping | is a macro specifying the peripheral assignment for a channel. |

This function assigns a peripheral mapping to a uDMA channel. It is used to select which peripheral is used for a uDMA channel. The parameter ui32Mapping should be one of the macros named UDMA_CHn_tttt from the header file udma.h. For example, to assign uDMA channel 0 to the UART2 RX channel, the parameter should be the macro UDMA_CH0_UART2RX.

Please consult the Tiva data sheet for a table showing all the possible peripheral assignments for the uDMA channels for a particular device.

Definition at line 1224 of file udma.c.

References ASSERT, HWREG, and UDMA_CHMAP0.

| void uDMAChannelAttributeDisable | ( | uint32_t | ui32ChannelNum, |

| uint32_t | ui32Attr | ||

| ) |

Disables attributes of a uDMA channel.

| ui32ChannelNum | is the channel to configure. |

| ui32Attr | is a combination of attributes for the channel. |

This function is used to disable attributes of a uDMA channel.

The ui32Attr parameter is the logical OR of any of the following:

Definition at line 429 of file udma.c.

References ASSERT, HWREG, UDMA_ALTCLR, UDMA_ATTR_ALTSELECT, UDMA_ATTR_HIGH_PRIORITY, UDMA_ATTR_REQMASK, UDMA_ATTR_USEBURST, UDMA_PRIOCLR, UDMA_REQMASKCLR, and UDMA_USEBURSTCLR.

| void uDMAChannelAttributeEnable | ( | uint32_t | ui32ChannelNum, |

| uint32_t | ui32Attr | ||

| ) |

Enables attributes of a uDMA channel.

| ui32ChannelNum | is the channel to configure. |

| ui32Attr | is a combination of attributes for the channel. |

This function is used to enable attributes of a uDMA channel.

The ui32Attr parameter is the logical OR of any of the following:

Definition at line 356 of file udma.c.

References ASSERT, HWREG, UDMA_ALTSET, UDMA_ATTR_ALTSELECT, UDMA_ATTR_HIGH_PRIORITY, UDMA_ATTR_REQMASK, UDMA_ATTR_USEBURST, UDMA_PRIOSET, UDMA_REQMASKSET, and UDMA_USEBURSTSET.

| uint32_t uDMAChannelAttributeGet | ( | uint32_t | ui32ChannelNum | ) |

Gets the enabled attributes of a uDMA channel.

| ui32ChannelNum | is the channel to configure. |

This function returns a combination of flags representing the attributes of the uDMA channel.

Definition at line 500 of file udma.c.

References ASSERT, HWREG, UDMA_ALTSET, UDMA_ATTR_ALTSELECT, UDMA_ATTR_HIGH_PRIORITY, UDMA_ATTR_REQMASK, UDMA_ATTR_USEBURST, UDMA_PRIOSET, UDMA_REQMASKSET, and UDMA_USEBURSTSET.

| void uDMAChannelControlSet | ( | uint32_t | ui32ChannelStructIndex, |

| uint32_t | ui32Control | ||

| ) |

Sets the control parameters for a uDMA channel control structure.

| ui32ChannelStructIndex | is the logical OR of the uDMA channel number with UDMA_PRI_SELECT or UDMA_ALT_SELECT. |

| ui32Control | is logical OR of several control values to set the control parameters for the channel. |

This function is used to set control parameters for a uDMA transfer. These parameters are typically not changed often.

The ui32ChannelStructIndex parameter should be the logical OR of the channel number with one of UDMA_PRI_SELECT or UDMA_ALT_SELECT to choose whether the primary or alternate data structure is used.

The ui32Control parameter is the logical OR of five values: the data size, the source address increment, the destination address increment, the arbitration size, and the use burst flag. The choices available for each of these values is described below.

Choose the data size from one of UDMA_SIZE_8, UDMA_SIZE_16, or UDMA_SIZE_32 to select a data size of 8, 16, or 32 bits.

Choose the source address increment from one of UDMA_SRC_INC_8, UDMA_SRC_INC_16, UDMA_SRC_INC_32, or UDMA_SRC_INC_NONE to select an address increment of 8-bit bytes, 16-bit half-words, 32-bit words, or to select non-incrementing.

Choose the destination address increment from one of UDMA_DST_INC_8, UDMA_DST_INC_16, UDMA_DST_INC_32, or UDMA_DST_INC_NONE to select an address increment of 8-bit bytes, 16-bit half-words, 32-bit words, or to select non-incrementing.

The arbitration size determines how many items are transferred before the uDMA controller re-arbitrates for the bus. Choose the arbitration size from one of UDMA_ARB_1, UDMA_ARB_2, UDMA_ARB_4, UDMA_ARB_8, through UDMA_ARB_1024 to select the arbitration size from 1 to 1024 items, in powers of 2.

The value UDMA_NEXT_USEBURST is used to force the channel to only respond to burst requests at the tail end of a scatter-gather transfer.

Definition at line 603 of file udma.c.

References ASSERT, HWREG, UDMA_CHCTL_ARBSIZE_M, UDMA_CHCTL_DSTINC_M, UDMA_CHCTL_DSTSIZE_M, UDMA_CHCTL_NXTUSEBURST, UDMA_CHCTL_SRCINC_M, UDMA_CHCTL_SRCSIZE_M, UDMA_CTLBASE, and tDMAControlTable::ui32Control.

| void uDMAChannelDisable | ( | uint32_t | ui32ChannelNum | ) |

Disables a uDMA channel for operation.

| ui32ChannelNum | is the channel number to disable. |

This function disables a specific uDMA channel. Once disabled, a channel cannot respond to uDMA transfer requests until re-enabled via uDMAChannelEnable().

Definition at line 179 of file udma.c.

References ASSERT, HWREG, and UDMA_ENACLR.

| void uDMAChannelEnable | ( | uint32_t | ui32ChannelNum | ) |

Enables a uDMA channel for operation.

| ui32ChannelNum | is the channel number to enable. |

This function enables a specific uDMA channel for use. This function must be used to enable a channel before it can be used to perform a uDMA transfer.

When a uDMA transfer is completed, the channel is automatically disabled by the uDMA controller. Therefore, this function should be called prior to starting up any new transfer.

Definition at line 152 of file udma.c.

References ASSERT, HWREG, and UDMA_ENASET.

| bool uDMAChannelIsEnabled | ( | uint32_t | ui32ChannelNum | ) |

Checks if a uDMA channel is enabled for operation.

| ui32ChannelNum | is the channel number to check. |

This function checks to see if a specific uDMA channel is enabled. This function can be used to check the status of a transfer, as the channel is automatically disabled at the end of a transfer.

Definition at line 206 of file udma.c.

References ASSERT, HWREG, and UDMA_ENASET.

| uint32_t uDMAChannelModeGet | ( | uint32_t | ui32ChannelStructIndex | ) |

Gets the transfer mode for a uDMA channel control structure.

| ui32ChannelStructIndex | is the logical OR of the uDMA channel number with either UDMA_PRI_SELECT or UDMA_ALT_SELECT. |

This function is used to get the transfer mode for the uDMA channel and to query the status of a transfer on a channel. When the transfer is complete the mode is UDMA_MODE_STOP.

Definition at line 1018 of file udma.c.

References ASSERT, HWREG, UDMA_CHCTL_XFERMODE_M, UDMA_CTLBASE, UDMA_MODE_ALT_SELECT, UDMA_MODE_MEM_SCATTER_GATHER, UDMA_MODE_PER_SCATTER_GATHER, and tDMAControlTable::ui32Control.

| void uDMAChannelRequest | ( | uint32_t | ui32ChannelNum | ) |

Requests a uDMA channel to start a transfer.

| ui32ChannelNum | is the channel number on which to request a uDMA transfer. |

This function allows software to request a uDMA channel to begin a transfer. This function could be used for performing a memory-to-memory transfer, or if for some reason a transfer needs to be initiated by software instead of the peripheral associated with that channel.

Definition at line 320 of file udma.c.

References ASSERT, HWREG, and UDMA_SWREQ.

| void uDMAChannelScatterGatherSet | ( | uint32_t | ui32ChannelNum, |

| uint32_t | ui32TaskCount, | ||

| void * | pvTaskList, | ||

| uint32_t | ui32IsPeriphSG | ||

| ) |

Configures a uDMA channel for scatter-gather mode.

| ui32ChannelNum | is the uDMA channel number. |

| ui32TaskCount | is the number of scatter-gather tasks to execute. |

| pvTaskList | is a pointer to the beginning of the scatter-gather task list. |

| ui32IsPeriphSG | is a flag to indicate it is a peripheral scatter-gather transfer (else it is memory scatter-gather transfer) |

This function is used to configure a channel for scatter-gather mode. The caller must have already set up a task list and must pass a pointer to the start of the task list as the pvTaskList parameter. The ui32TaskCount parameter is the count of tasks in the task list, not the size of the task list. The flag bIsPeriphSG should be used to indicate if scatter-gather should be configured for peripheral or memory operation.

Definition at line 861 of file udma.c.

References ASSERT, HWREG, tDMAControlTable::pvDstEndAddr, tDMAControlTable::pvSrcEndAddr, UDMA_ALT_SELECT, UDMA_ALTCLR, UDMA_CHCTL_ARBSIZE_4, UDMA_CHCTL_DSTINC_32, UDMA_CHCTL_DSTSIZE_32, UDMA_CHCTL_SRCINC_32, UDMA_CHCTL_SRCSIZE_32, UDMA_CHCTL_XFERMODE_MEM_SG, UDMA_CHCTL_XFERMODE_PER_SG, UDMA_CHCTL_XFERSIZE_S, UDMA_CTLBASE, tDMAControlTable::ui32Control, and tDMAControlTable::ui32Spare.

| void uDMAChannelSelectDefault | ( | uint32_t | ui32DefPeriphs | ) |

Selects the default peripheral for a set of uDMA channels.

| ui32DefPeriphs | is the logical OR of the uDMA channels for which to use the default peripheral, instead of the secondary peripheral. |

This function is used to select the default peripheral assignment for a set of uDMA channels.

The parameter ui32DefPeriphs can be the logical OR of any of the following macros. If one of the macros below is in the list passed to this function, then the default peripheral (marked as DEF) is selected.

Definition at line 1370 of file udma.c.

References HWREG, and UDMA_CHASGN.

| void uDMAChannelSelectSecondary | ( | uint32_t | ui32SecPeriphs | ) |

Selects the secondary peripheral for a set of uDMA channels.

| ui32SecPeriphs | is the logical OR of the uDMA channels for which to use the secondary peripheral, instead of the default peripheral. |

This function is used to select the secondary peripheral assignment for a set of uDMA channels. By selecting the secondary peripheral assignment for a channel, the default peripheral assignment is no longer available for that channel.

The parameter ui32SecPeriphs can be the logical OR of any of the following macros. If one of the macros below is in the list passed to this function, then the secondary peripheral (marked as SEC) is selected.

Definition at line 1313 of file udma.c.

References HWREG, and UDMA_CHASGN.

| uint32_t uDMAChannelSizeGet | ( | uint32_t | ui32ChannelStructIndex | ) |

Gets the current transfer size for a uDMA channel control structure.

| ui32ChannelStructIndex | is the logical OR of the uDMA channel number with either UDMA_PRI_SELECT or UDMA_ALT_SELECT. |

This function is used to get the uDMA transfer size for a channel. The transfer size is the number of items to transfer, where the size of an item might be 8, 16, or 32 bits. If a partial transfer has already occurred, then the number of remaining items is returned. If the transfer is complete, then 0 is returned.

Definition at line 948 of file udma.c.

References ASSERT, HWREG, UDMA_CHCTL_XFERMODE_M, UDMA_CHCTL_XFERSIZE_M, UDMA_CTLBASE, and tDMAControlTable::ui32Control.

| void uDMAChannelTransferSet | ( | uint32_t | ui32ChannelStructIndex, |

| uint32_t | ui32Mode, | ||

| void * | pvSrcAddr, | ||

| void * | pvDstAddr, | ||

| uint32_t | ui32TransferSize | ||

| ) |

Sets the transfer parameters for a uDMA channel control structure.

| ui32ChannelStructIndex | is the logical OR of the uDMA channel number with either UDMA_PRI_SELECT or UDMA_ALT_SELECT. |

| ui32Mode | is the type of uDMA transfer. |

| pvSrcAddr | is the source address for the transfer. |

| pvDstAddr | is the destination address for the transfer. |

| ui32TransferSize | is the number of data items to transfer. |

This function is used to configure the parameters for a uDMA transfer. These parameters are not typically changed often. The function uDMAChannelControlSet() MUST be called at least once for this channel prior to calling this function.

The ui32ChannelStructIndex parameter should be the logical OR of the channel number with one of UDMA_PRI_SELECT or UDMA_ALT_SELECT to choose whether the primary or alternate data structure is used.

The ui32Mode parameter should be one of the following values:

The pvSrcAddr and pvDstAddr parameters are pointers to the first location of the data to be transferred. These addresses should be aligned according to the item size. The compiler takes care of this alignment if the pointers are pointing to storage of the appropriate data type.

The ui32TransferSize parameter is the number of data items, not the number of bytes.

The two scatter-gather modes, memory and peripheral, are actually different depending on whether the primary or alternate control structure is selected. This function looks for the UDMA_PRI_SELECT and UDMA_ALT_SELECT flag along with the channel number and sets the scatter-gather mode as appropriate for the primary or alternate control structure.

The channel must also be enabled using uDMAChannelEnable() after calling this function. The transfer does not begin until the channel has been configured and enabled. Note that the channel is automatically disabled after the transfer is completed, meaning that uDMAChannelEnable() must be called again after setting up the next transfer.

Definition at line 710 of file udma.c.

References ASSERT, HWREG, tDMAControlTable::pvDstEndAddr, tDMAControlTable::pvSrcEndAddr, UDMA_ALT_SELECT, UDMA_CHCTL_DSTINC_M, UDMA_CHCTL_SRCINC_M, UDMA_CHCTL_XFERMODE_M, UDMA_CHCTL_XFERSIZE_M, UDMA_CTLBASE, UDMA_DST_INC_NONE, UDMA_MODE_ALT_SELECT, UDMA_MODE_MEM_SCATTER_GATHER, UDMA_MODE_PER_SCATTER_GATHER, UDMA_SRC_INC_NONE, and tDMAControlTable::ui32Control.

| void* uDMAControlAlternateBaseGet | ( | void | ) |

Gets the base address for the channel control table alternate structures.

This function gets the base address of the second half of the channel control table that holds the alternate control structures for each channel.

Definition at line 290 of file udma.c.

References HWREG, and UDMA_ALTBASE.

| void* uDMAControlBaseGet | ( | void | ) |

Gets the base address for the channel control table.

This function gets the base address of the channel control table. This table resides in system memory and holds control information for each uDMA channel.

Definition at line 269 of file udma.c.

References HWREG, and UDMA_CTLBASE.

| void uDMAControlBaseSet | ( | void * | psControlTable | ) |

Sets the base address for the channel control table.

| psControlTable | is a pointer to the 1024-byte-aligned base address of the uDMA channel control table. |

This function configures the base address of the channel control table. This table resides in system memory and holds control information for each uDMA channel. The table must be aligned on a 1024-byte boundary. The base address must be configured before any of the channel functions can be used.

The size of the channel control table depends on the number of uDMA channels and the transfer modes that are used. Refer to the introductory text and the microcontroller datasheet for more information about the channel control table.

Definition at line 242 of file udma.c.

References ASSERT, HWREG, and UDMA_CTLBASE.

| void uDMADisable | ( | void | ) |

Disables the uDMA controller for use.

This function disables the uDMA controller. Once disabled, the uDMA controller cannot operate until re-enabled with uDMAEnable().

Definition at line 86 of file udma.c.

References HWREG, and UDMA_CFG.

| void uDMAEnable | ( | void | ) |

Enables the uDMA controller for use.

This function enables the uDMA controller. The uDMA controller must be enabled before it can be configured and used.

Definition at line 67 of file udma.c.

References HWREG, UDMA_CFG, and UDMA_CFG_MASTEN.

| void uDMAErrorStatusClear | ( | void | ) |

Clears the uDMA error interrupt.

This function clears a pending uDMA error interrupt. This function should be called from within the uDMA error interrupt handler to clear the interrupt.

Definition at line 126 of file udma.c.

References HWREG, and UDMA_ERRCLR.

| uint32_t uDMAErrorStatusGet | ( | void | ) |

Gets the uDMA error status.

This function returns the uDMA error status. It should be called from within the uDMA error interrupt handler to determine if a uDMA error occurred.

Definition at line 106 of file udma.c.

References HWREG, and UDMA_ERRCLR.

| void uDMAIntClear | ( | uint32_t | ui32ChanMask | ) |

Clears uDMA interrupt status.

| ui32ChanMask | is a 32-bit mask with one bit for each uDMA channel. |

This function clears bits in the uDMA interrupt status register according to which bits are set in ui32ChanMask. There is one bit for each channel. If a a bit is set in ui32ChanMask, then that corresponding channel's interrupt status is cleared (if it was set).

Definition at line 1191 of file udma.c.

References HWREG, and UDMA_CHIS.

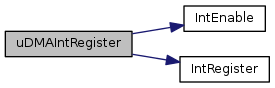

| void uDMAIntRegister | ( | uint32_t | ui32IntChannel, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the uDMA controller.

| ui32IntChannel | identifies which uDMA interrupt is to be registered. |

| pfnHandler | is a pointer to the function to be called when the interrupt is activated. |

This function registers and enables the handler to be called when the uDMA controller generates an interrupt. The ui32IntChannel parameter should be one of the following:

Definition at line 1092 of file udma.c.

References ASSERT, IntEnable(), IntRegister(), UDMA_INT_ERR, and UDMA_INT_SW.

| uint32_t uDMAIntStatus | ( | void | ) |

Gets the uDMA controller channel interrupt status.

This function is used to get the interrupt status of the uDMA controller. The returned value is a 32-bit bit mask that indicates which channels are requesting an interrupt. This function can be used from within an interrupt handler to determine or confirm which uDMA channel has requested an interrupt.

Definition at line 1163 of file udma.c.

References HWREG, and UDMA_CHIS.

| void uDMAIntUnregister | ( | uint32_t | ui32IntChannel | ) |

Unregisters an interrupt handler for the uDMA controller.

| ui32IntChannel | identifies which uDMA interrupt to unregister. |

This function disables and unregisters the handler to be called for the specified uDMA interrupt. The ui32IntChannel parameter should be one of UDMA_INT_SW or UDMA_INT_ERR as documented for the function uDMAIntRegister().

Definition at line 1130 of file udma.c.

References IntDisable(), and IntUnregister().