|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Macros | |

| #define | NUM_INTERRUPTS 155 |

Functions | |

| static void | _IntDefaultHandler (void) |

| static | __attribute__ ((section("vtable"))) |

| bool | IntMasterDisable (void) |

| void | IntRegister (uint32_t ui32Interrupt, void(*pfnHandler)(void)) |

| void | IntUnregister (uint32_t ui32Interrupt) |

| void | IntPriorityGroupingSet (uint32_t ui32Bits) |

| uint32_t | IntPriorityGroupingGet (void) |

| void | IntPrioritySet (uint32_t ui32Interrupt, uint8_t ui8Priority) |

| int32_t | IntPriorityGet (uint32_t ui32Interrupt) |

| void | IntEnable (uint32_t ui32Interrupt) |

| void | IntDisable (uint32_t ui32Interrupt) |

| uint32_t | IntIsEnabled (uint32_t ui32Interrupt) |

| void | IntPendSet (uint32_t ui32Interrupt) |

| void | IntPendClear (uint32_t ui32Interrupt) |

| void | IntPriorityMaskSet (uint32_t ui32PriorityMask) |

| uint32_t | IntPriorityMaskGet (void) |

| void | IntTrigger (uint32_t ui32Interrupt) |

Variables | |

| static const uint32_t | g_pui32Priority [] |

| static const uint32_t | g_pui32Regs [] |

| static const uint32_t | g_pui32EnRegs [] |

| static const uint32_t | g_pui32Dii16Regs [] |

| static const uint32_t | g_pui32PendRegs [] |

| static const uint32_t | g_pui32UnpendRegs [] |

| #define NUM_INTERRUPTS 155 |

Definition at line 172 of file interrupt.c.

Referenced by IntDisable(), IntEnable(), IntIsEnabled(), IntPendClear(), IntPendSet(), IntPriorityGet(), IntPrioritySet(), IntRegister(), IntTrigger(), and IntUnregister().

|

static |

Enables the processor interrupt.

This function allows the processor to respond to interrupts. This function does not affect the set of interrupts enabled in the interrupt controller; it just gates the single interrupt from the controller to the processor.

Example: Enable interrupts to the processor.

//! // //! // Enable interrupts to the processor. //! // //! IntMasterEnable(); //! //!

\return Returns \b true if interrupts were disabled when the function was called or \b false if they were initially enabled.

Definition at line 184 of file interrupt.c.

References CPUcpsie().

|

static |

Definition at line 147 of file interrupt.c.

Referenced by IntUnregister().

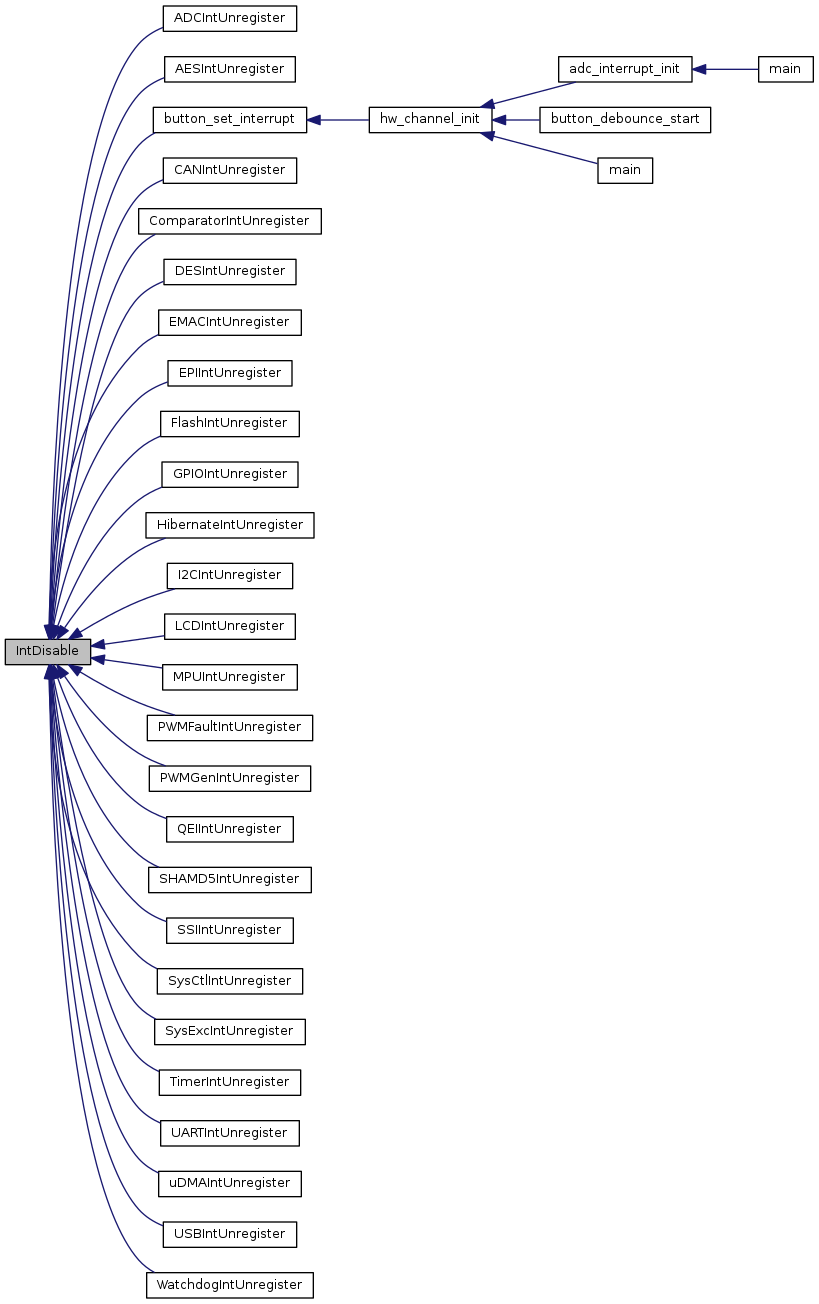

| void IntDisable | ( | uint32_t | ui32Interrupt | ) |

Disables an interrupt.

| ui32Interrupt | specifies the interrupt to be disabled. |

The specified interrupt is disabled in the interrupt controller. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. Other enables for the interrupt (such as at the peripheral level) are unaffected by this function.

Example: Disable the UART 0 interrupt.

//! // //! // Disable the UART 0 interrupt in the interrupt controller. //! // //! IntDisable(INT_UART0); //! //!

\return None.

Definition at line 684 of file interrupt.c.

References ASSERT, FAULT_BUS, FAULT_MPU, FAULT_SYSTICK, FAULT_USAGE, g_pui32Dii16Regs, HWREG, NUM_INTERRUPTS, NVIC_ST_CTRL, NVIC_ST_CTRL_INTEN, NVIC_SYS_HND_CTRL, NVIC_SYS_HND_CTRL_BUS, NVIC_SYS_HND_CTRL_MEM, and NVIC_SYS_HND_CTRL_USAGE.

Referenced by ADCIntUnregister(), AESIntUnregister(), button_set_interrupt(), CANIntUnregister(), ComparatorIntUnregister(), DESIntUnregister(), EMACIntUnregister(), EPIIntUnregister(), FlashIntUnregister(), GPIOIntUnregister(), HibernateIntUnregister(), I2CIntUnregister(), LCDIntUnregister(), MPUIntUnregister(), PWMFaultIntUnregister(), PWMGenIntUnregister(), QEIIntUnregister(), SHAMD5IntUnregister(), SSIIntUnregister(), SysCtlIntUnregister(), SysExcIntUnregister(), TimerIntUnregister(), UARTIntUnregister(), uDMAIntUnregister(), USBIntUnregister(), and WatchdogIntUnregister().

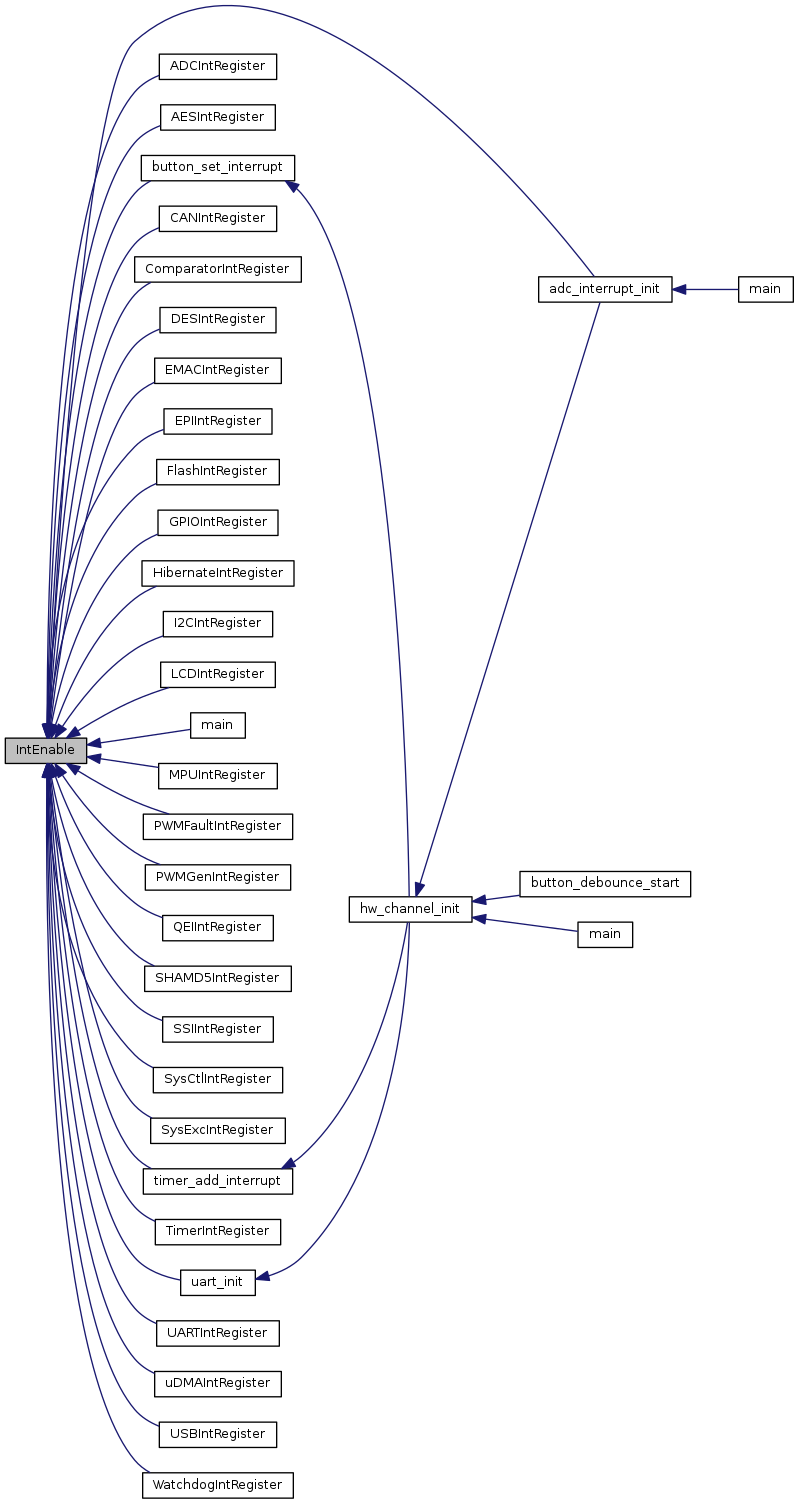

| void IntEnable | ( | uint32_t | ui32Interrupt | ) |

Enables an interrupt.

| ui32Interrupt | specifies the interrupt to be enabled. |

The specified interrupt is enabled in the interrupt controller. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. Other enables for the interrupt (such as at the peripheral level) are unaffected by this function.

Example: Enable the UART 0 interrupt.

//! // //! // Enable the UART 0 interrupt in the interrupt controller. //! // //! IntEnable(INT_UART0); //! //!

\return None.

Definition at line 610 of file interrupt.c.

References ASSERT, FAULT_BUS, FAULT_MPU, FAULT_SYSTICK, FAULT_USAGE, g_pui32EnRegs, HWREG, NUM_INTERRUPTS, NVIC_ST_CTRL, NVIC_ST_CTRL_INTEN, NVIC_SYS_HND_CTRL, NVIC_SYS_HND_CTRL_BUS, NVIC_SYS_HND_CTRL_MEM, and NVIC_SYS_HND_CTRL_USAGE.

Referenced by adc_interrupt_init(), ADCIntRegister(), AESIntRegister(), button_set_interrupt(), CANIntRegister(), ComparatorIntRegister(), DESIntRegister(), EMACIntRegister(), EPIIntRegister(), FlashIntRegister(), GPIOIntRegister(), HibernateIntRegister(), I2CIntRegister(), LCDIntRegister(), main(), MPUIntRegister(), PWMFaultIntRegister(), PWMGenIntRegister(), QEIIntRegister(), SHAMD5IntRegister(), SSIIntRegister(), SysCtlIntRegister(), SysExcIntRegister(), timer_add_interrupt(), TimerIntRegister(), uart_init(), UARTIntRegister(), uDMAIntRegister(), USBIntRegister(), and WatchdogIntRegister().

| uint32_t IntIsEnabled | ( | uint32_t | ui32Interrupt | ) |

Returns if a peripheral interrupt is enabled.

| ui32Interrupt | specifies the interrupt to check. |

This function checks if the specified interrupt is enabled in the interrupt controller. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file.

Example: Disable the UART 0 interrupt if it is enabled.

//! //

//! // Disable the UART 0 interrupt if it is enabled.

//! //

//! if(IntIsEnabled(INT_UART0))

//! {

//! IntDisable(INT_UART0);

//! }

//! \return A non-zero value if the interrupt is enabled.

Definition at line 759 of file interrupt.c.

References ASSERT, FAULT_BUS, FAULT_MPU, FAULT_SYSTICK, FAULT_USAGE, g_pui32EnRegs, HWREG, NUM_INTERRUPTS, NVIC_ST_CTRL, NVIC_ST_CTRL_INTEN, NVIC_SYS_HND_CTRL, NVIC_SYS_HND_CTRL_BUS, NVIC_SYS_HND_CTRL_MEM, and NVIC_SYS_HND_CTRL_USAGE.

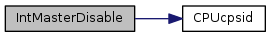

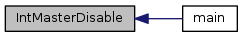

| bool IntMasterDisable | ( | void | ) |

Disables the processor interrupt.

This function prevents the processor from receiving interrupts. This function does not affect the set of interrupts enabled in the interrupt controller; it just gates the single interrupt from the controller to the processor.

interrupt.h and call this function without having included hw_types.h. Now that the return is a bool, a compiler error occurs in this case. The solution is to include hw_types.h before including interrupt.h.Example: Disable interrupts to the processor.

//! // //! // Disable interrupts to the processor. //! // //! IntMasterDisable(); //! //!

\return Returns \b true if interrupts were already disabled when the function was called or \b false if they were initially enabled.

Definition at line 249 of file interrupt.c.

References CPUcpsid().

Referenced by main().

| void IntPendClear | ( | uint32_t | ui32Interrupt | ) |

Un-pends an interrupt.

| ui32Interrupt | specifies the interrupt to be un-pended. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. |

The specified interrupt is un-pended in the interrupt controller. This causes any previously generated interrupts that have not been handled yet (due to higher priority interrupts or the interrupt not having been enabled yet) to be discarded.

Example: Un-pend a UART 0 interrupt.

//! // //! // Un-pend a UART 0 interrupt. //! // //! IntPendClear(INT_UART0); //!

\return None.

Definition at line 912 of file interrupt.c.

References ASSERT, FAULT_PENDSV, FAULT_SYSTICK, g_pui32UnpendRegs, HWREG, NUM_INTERRUPTS, NVIC_INT_CTRL, NVIC_INT_CTRL_PENDSTCLR, and NVIC_INT_CTRL_UNPEND_SV.

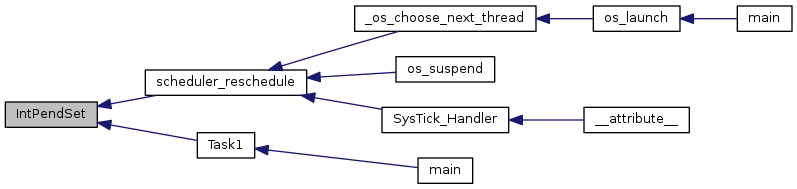

| void IntPendSet | ( | uint32_t | ui32Interrupt | ) |

Pends an interrupt.

| ui32Interrupt | specifies the interrupt to be pended. |

The specified interrupt is pended in the interrupt controller. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. Pending an interrupt causes the interrupt controller to execute the corresponding interrupt handler at the next available time, based on the current interrupt state priorities. For example, if called by a higher priority interrupt handler, the specified interrupt handler is not called until after the current interrupt handler has completed execution. The interrupt must have been enabled for it to be called.

Example: Pend a UART 0 interrupt.

//! // //! // Pend a UART 0 interrupt. //! // //! IntPendSet(INT_UART0); //!

\return None.

Definition at line 844 of file interrupt.c.

References ASSERT, FAULT_NMI, FAULT_PENDSV, FAULT_SYSTICK, g_pui32PendRegs, HWREG, NUM_INTERRUPTS, NVIC_INT_CTRL, NVIC_INT_CTRL_NMI_SET, NVIC_INT_CTRL_PEND_SV, and NVIC_INT_CTRL_PENDSTSET.

Referenced by scheduler_reschedule(), and Task1().

| int32_t IntPriorityGet | ( | uint32_t | ui32Interrupt | ) |

Gets the priority of an interrupt.

| ui32Interrupt | specifies the interrupt in question. |

This function gets the priority of an interrupt. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. See IntPrioritySet() for a full definition of the priority value.

Example: Get the current UART 0 interrupt priority.

//! // //! // Get the current UART 0 interrupt priority. //! // //! IntPriorityGet(INT_UART0); //! //!

\return Returns the interrupt priority for the given interrupt.

Definition at line 570 of file interrupt.c.

References ASSERT, g_pui32Regs, HWREG, and NUM_INTERRUPTS.

| uint32_t IntPriorityGroupingGet | ( | void | ) |

Gets the priority grouping of the interrupt controller.

This function returns the split between preemptable priority levels and sub-priority levels in the interrupt priority specification.

Example: Get the priority grouping for the interrupt controller.

//! // //! // Get the priority grouping for the interrupt controller. //! // //! IntPriorityGroupingGet(); //! //!

\return The number of bits of preemptable priority.

Definition at line 455 of file interrupt.c.

References g_pui32Priority, HWREG, NUM_PRIORITY, NVIC_APINT, and NVIC_APINT_PRIGROUP_M.

| void IntPriorityGroupingSet | ( | uint32_t | ui32Bits | ) |

Sets the priority grouping of the interrupt controller.

| ui32Bits | specifies the number of bits of preemptable priority. |

This function specifies the split between preemptable priority levels and sub-priority levels in the interrupt priority specification. The range of the grouping values are dependent upon the hardware implementation; on the Tiva C and E Series family, three bits are available for hardware interrupt prioritization and therefore priority grouping values of three through seven have the same effect.

Example: Set the priority grouping for the interrupt controller.

//! // //! // Set the priority grouping for the interrupt controller to 2 bits. //! // //! IntPriorityGroupingSet(2); //! //!

\return None.

Definition at line 421 of file interrupt.c.

References ASSERT, g_pui32Priority, HWREG, NUM_PRIORITY, NVIC_APINT, and NVIC_APINT_VECTKEY.

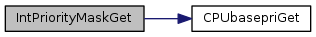

| uint32_t IntPriorityMaskGet | ( | void | ) |

Gets the priority masking level

This function gets the current setting of the interrupt priority masking level. The value returned is the priority level such that all interrupts of that and lesser priority are masked. A value of 0 means that priority masking is disabled.

Smaller numbers correspond to higher interrupt priorities. So for example a priority level mask of 4 allows interrupts of priority level 0-3, and interrupts with a numerical priority of 4 and greater are blocked.

The hardware priority mechanism only looks at the upper 3 bits of the priority level, so any prioritization must be performed in those bits.

Example: Get the current interrupt priority mask.

//! // //! // Get the current interrupt priority mask. //! // //! IntPriorityMaskGet(); //!

\return Returns the value of the interrupt priority level mask.

Definition at line 1015 of file interrupt.c.

References CPUbasepriGet().

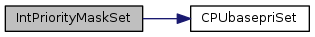

| void IntPriorityMaskSet | ( | uint32_t | ui32PriorityMask | ) |

Sets the priority masking level

| ui32PriorityMask | is the priority level that is masked. |

This function sets the interrupt priority masking level so that all interrupts at the specified or lesser priority level are masked. Masking interrupts can be used to globally disable a set of interrupts with priority below a predetermined threshold. A value of 0 disables priority masking.

Smaller numbers correspond to higher interrupt priorities. So for example a priority level mask of 4 allows interrupts of priority level 0-3, and interrupts with a numerical priority of 4 and greater are blocked.

Example: Mask of interrupt priorities greater than or equal to 0x80.

//! // //! // Mask of interrupt priorities greater than or equal to 0x80. //! // //! IntPriorityMaskSet(0x80); //!

\return None.

Definition at line 978 of file interrupt.c.

References CPUbasepriSet().

| void IntPrioritySet | ( | uint32_t | ui32Interrupt, |

| uint8_t | ui8Priority | ||

| ) |

Sets the priority of an interrupt.

| ui32Interrupt | specifies the interrupt in question. |

| ui8Priority | specifies the priority of the interrupt. |

This function is used to set the priority of an interrupt. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. The ui8Priority parameter specifies the interrupts hardware priority level of the interrupt in the interrupt controller. When multiple interrupts are asserted simultaneously, the ones with the highest priority are processed before the lower priority interrupts. Smaller numbers correspond to higher interrupt priorities; priority 0 is the highest interrupt priority.

Example: Set priorities for UART 0 and USB interrupts.

//! // //! // Set the UART 0 interrupt priority to the lowest priority. //! // //! IntPrioritySet(INT_UART0, 0xE0); //! //! // //! // Set the USB 0 interrupt priority to the highest priority. //! // //! IntPrioritySet(INT_USB0, 0); //! //!

\return None.

Definition at line 527 of file interrupt.c.

References ASSERT, g_pui32Regs, HWREG, and NUM_INTERRUPTS.

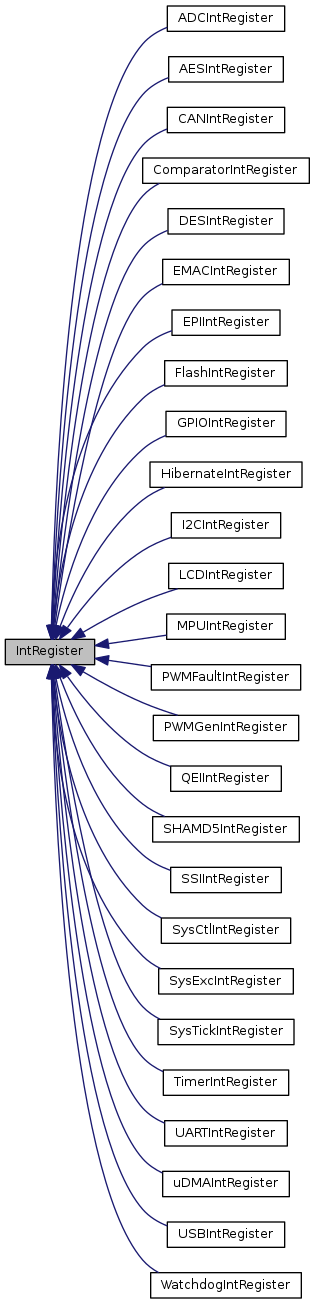

| void IntRegister | ( | uint32_t | ui32Interrupt, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers a function to be called when an interrupt occurs.

| ui32Interrupt | specifies the interrupt in question. |

| pfnHandler | is a pointer to the function to be called. |

This function is used to specify the handler function to be called when the given interrupt is asserted to the processor. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. When the interrupt occurs, if it is enabled (via IntEnable()), the handler function is called in interrupt context. Because the handler function can preempt other code, care must be taken to protect memory or peripherals that are accessed by the handler and other non-handler code.

Example: Set the UART 0 interrupt handler.

//!

//! //

//! // UART 0 interrupt handler.

//! //

//! void

//! UART0Handler(void)

//! {

//! //

//! // Handle interrupt.

//! //

//! }

//!

//! //

//! // Set the UART 0 interrupt handler.

//! //

//! IntRegister(INT_UART0, UART0Handler);

//!

//! \return None.

Definition at line 309 of file interrupt.c.

References ASSERT, HWREG, NUM_INTERRUPTS, and NVIC_VTABLE.

Referenced by ADCIntRegister(), AESIntRegister(), CANIntRegister(), ComparatorIntRegister(), DESIntRegister(), EMACIntRegister(), EPIIntRegister(), FlashIntRegister(), GPIOIntRegister(), HibernateIntRegister(), I2CIntRegister(), LCDIntRegister(), MPUIntRegister(), PWMFaultIntRegister(), PWMGenIntRegister(), QEIIntRegister(), SHAMD5IntRegister(), SSIIntRegister(), SysCtlIntRegister(), SysExcIntRegister(), SysTickIntRegister(), TimerIntRegister(), UARTIntRegister(), uDMAIntRegister(), USBIntRegister(), and WatchdogIntRegister().

| void IntTrigger | ( | uint32_t | ui32Interrupt | ) |

Triggers an interrupt.

| ui32Interrupt | specifies the interrupt to be triggered. |

This function performs a software trigger of an interrupt. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. The interrupt controller behaves as if the corresponding interrupt line was asserted, and the interrupt is handled in the same manner (meaning that it must be enabled in order to be processed, and the processing is based on its priority with respect to other unhandled interrupts).

Definition at line 1042 of file interrupt.c.

References ASSERT, HWREG, NUM_INTERRUPTS, and NVIC_SW_TRIG.

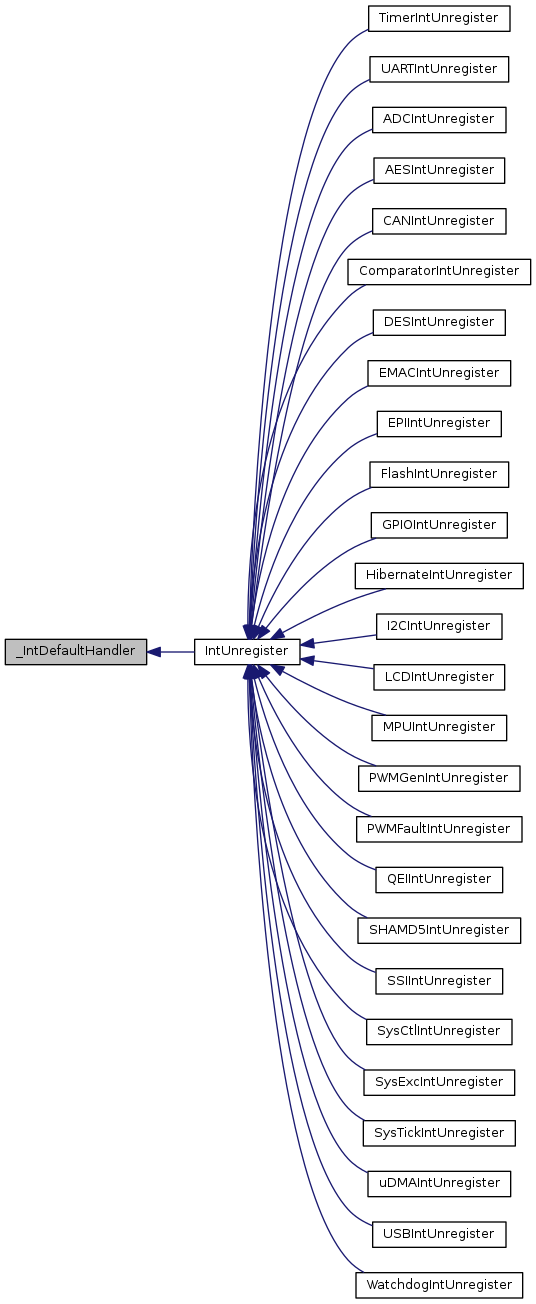

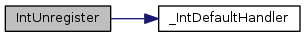

| void IntUnregister | ( | uint32_t | ui32Interrupt | ) |

Unregisters the function to be called when an interrupt occurs.

| ui32Interrupt | specifies the interrupt in question. |

This function is used to indicate that no handler is called when the given interrupt is asserted to the processor. The ui32Interrupt parameter must be one of the valid INT_* values listed in Peripheral Driver Library User's Guide and defined in the inc/hw_ints.h header file. The interrupt source is automatically disabled (via IntDisable()) if necessary.

Example: Reset the UART 0 interrupt handler to the default handler.

//! // //! // Reset the UART 0 interrupt handler to the default handler. //! // //! IntUnregister(INT_UART0); //! //!

\return None.

Definition at line 381 of file interrupt.c.

References _IntDefaultHandler(), ASSERT, and NUM_INTERRUPTS.

Referenced by ADCIntUnregister(), AESIntUnregister(), CANIntUnregister(), ComparatorIntUnregister(), DESIntUnregister(), EMACIntUnregister(), EPIIntUnregister(), FlashIntUnregister(), GPIOIntUnregister(), HibernateIntUnregister(), I2CIntUnregister(), LCDIntUnregister(), MPUIntUnregister(), PWMFaultIntUnregister(), PWMGenIntUnregister(), QEIIntUnregister(), SHAMD5IntUnregister(), SSIIntUnregister(), SysCtlIntUnregister(), SysExcIntUnregister(), SysTickIntUnregister(), TimerIntUnregister(), UARTIntUnregister(), uDMAIntUnregister(), USBIntUnregister(), and WatchdogIntUnregister().

|

static |

|

static |

Definition at line 93 of file interrupt.c.

Referenced by IntEnable(), and IntIsEnabled().

|

static |

|

static |

Definition at line 62 of file interrupt.c.

Referenced by IntPriorityGroupingGet(), and IntPriorityGroupingSet().

|

static |

Definition at line 75 of file interrupt.c.

Referenced by IntPriorityGet(), and IntPrioritySet().

|

static |