|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Functions | |

| void | AESReset (uint32_t ui32Base) |

| void | AESConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | AESKey1Set (uint32_t ui32Base, uint32_t *pui32Key, uint32_t ui32Keysize) |

| void | AESKey2Set (uint32_t ui32Base, uint32_t *pui32Key, uint32_t ui32Keysize) |

| void | AESKey3Set (uint32_t ui32Base, uint32_t *pui32Key) |

| void | AESIVSet (uint32_t ui32Base, uint32_t *pui32IVdata) |

| void | AESIVRead (uint32_t ui32Base, uint32_t *pui32IVData) |

| void | AESTagRead (uint32_t ui32Base, uint32_t *pui32TagData) |

| void | AESLengthSet (uint32_t ui32Base, uint64_t ui64Length) |

| void | AESAuthLengthSet (uint32_t ui32Base, uint32_t ui32Length) |

| bool | AESDataReadNonBlocking (uint32_t ui32Base, uint32_t *pui32Dest) |

| void | AESDataRead (uint32_t ui32Base, uint32_t *pui32Dest) |

| bool | AESDataWriteNonBlocking (uint32_t ui32Base, uint32_t *pui32Src) |

| void | AESDataWrite (uint32_t ui32Base, uint32_t *pui32Src) |

| bool | AESDataProcess (uint32_t ui32Base, uint32_t *pui32Src, uint32_t *pui32Dest, uint32_t ui32Length) |

| bool | AESDataAuth (uint32_t ui32Base, uint32_t *pui32Src, uint32_t ui32Length, uint32_t *pui32Tag) |

| bool | AESDataProcessAuth (uint32_t ui32Base, uint32_t *pui32Src, uint32_t *pui32Dest, uint32_t ui32Length, uint32_t *pui32AuthSrc, uint32_t ui32AuthLength, uint32_t *pui32Tag) |

| uint32_t | AESIntStatus (uint32_t ui32Base, bool bMasked) |

| void | AESIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | AESIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | AESIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | AESIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | AESIntUnregister (uint32_t ui32Base) |

| void | AESDMAEnable (uint32_t ui32Base, uint32_t ui32Flags) |

| void | AESDMADisable (uint32_t ui32Base, uint32_t ui32Flags) |

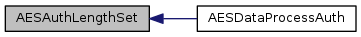

| void AESAuthLengthSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Length | ||

| ) |

Sets the authentication data length in the AES module.

| ui32Base | is the base address of the AES module. |

| ui32Length | is the length in bytes. |

This function is only used to write the authentication data length in the combined modes (GCM or CCM) and XTS mode. Supported AAD lengths for CCM are from 0 to (2^16 - 28) bytes. For GCM, any value up to (2^32 - 1) can be used. For XTS mode, this register is used to load j. Loading of j is only required if j != 0. j represents the sequential number of the 128-bit blocks inside the data unit. Consequently, j must be multiplied by 16 when passed to this function, thereby placing the block number in bits [31:4] of the register.

When this function is called, the engine is triggered to start using this context for GCM and CCM.

Definition at line 561 of file aes.c.

References AES_BASE, AES_O_AUTH_LENGTH, ASSERT, and HWREG.

Referenced by AESDataProcessAuth().

| void AESConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the AES module.

| ui32Base | is the base address of the AES module. |

| ui32Config | is the configuration of the AES module. |

This function configures the AES module based on the specified parameters. It does not change any DMA- or interrupt-related parameters.

The ui32Config parameter is a bit-wise OR of a number of configuration flags. The valid flags are grouped based on their function.

The direction of the operation is specified with only of following flags:

The key size is specified with only one of the following flags:

The mode of operation is specified with only one of the following flags.

The following defines are used to specify the counter width. It is only required to be defined when using CTR, CCM, or GCM modes, only one of the following defines must be used to specify the counter width length:

Only one of the following defines must be used to specify the length field for CCM operations (L):

Only one of the following defines must be used to specify the length of the authentication field for CCM operations (M) through the ui32Config argument in the AESConfigSet() function:

Definition at line 183 of file aes.c.

References AES_BASE, AES_CFG_CCM_L_1, AES_CFG_CCM_L_2, AES_CFG_CCM_L_3, AES_CFG_CCM_L_4, AES_CFG_CCM_L_5, AES_CFG_CCM_L_6, AES_CFG_CCM_L_7, AES_CFG_CCM_L_8, AES_CFG_CCM_M_10, AES_CFG_CCM_M_12, AES_CFG_CCM_M_14, AES_CFG_CCM_M_16, AES_CFG_CCM_M_4, AES_CFG_CCM_M_6, AES_CFG_CCM_M_8, AES_CFG_CTR_WIDTH_128, AES_CFG_CTR_WIDTH_32, AES_CFG_CTR_WIDTH_64, AES_CFG_CTR_WIDTH_96, AES_CFG_DIR_DECRYPT, AES_CFG_DIR_ENCRYPT, AES_CFG_KEY_SIZE_128BIT, AES_CFG_KEY_SIZE_192BIT, AES_CFG_KEY_SIZE_256BIT, AES_CFG_MODE_CBC, AES_CFG_MODE_CBCMAC, AES_CFG_MODE_CCM, AES_CFG_MODE_CFB, AES_CFG_MODE_CTR, AES_CFG_MODE_ECB, AES_CFG_MODE_F8, AES_CFG_MODE_F9, AES_CFG_MODE_GCM_HLY0CALC, AES_CFG_MODE_GCM_HLY0ZERO, AES_CFG_MODE_GCM_HY0CALC, AES_CFG_MODE_ICM, AES_CFG_MODE_XTS_K2IJL, AES_CFG_MODE_XTS_K2ILJ0, AES_CFG_MODE_XTS_TWEAKJL, AES_CTRL_SAVE_CONTEXT, AES_O_CTRL, ASSERT, and HWREG.

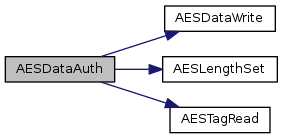

| bool AESDataAuth | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src, | ||

| uint32_t | ui32Length, | ||

| uint32_t * | pui32Tag | ||

| ) |

Used to authenticate blocks of data by generating a hash tag.

| ui32Base | is the base address of the AES module. |

| pui32Src | is a pointer to the memory location where the input data is stored. The data must be padded to the 16-byte boundary. |

| ui32Length | is the length of the cryptographic data in bytes. |

| pui32Tag | is a pointer to a 4-word array where the hash tag is written. |

This function processes data to produce a hash tag that can be used tor authentication. Before calling this function, ensure that the AES module is properly configured the key, data size, mode, etc. Only CBC-MAC and F9 modes should be used.

Definition at line 825 of file aes.c.

References AES_BASE, AESDataWrite(), AESLengthSet(), AESTagRead(), and ASSERT.

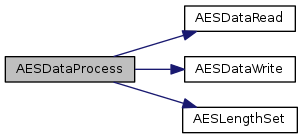

| bool AESDataProcess | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src, | ||

| uint32_t * | pui32Dest, | ||

| uint32_t | ui32Length | ||

| ) |

Used to process(transform) blocks of data, either encrypt or decrypt it.

| ui32Base | is the base address of the AES module. |

| pui32Src | is a pointer to the memory location where the input data is stored. The data must be padded to the 16-byte boundary. |

| pui32Dest | is a pointer to the memory location output is written. The space for written data must be rounded up to the 16-byte boundary. |

| ui32Length | is the length of the cryptographic data in bytes. |

This function iterates the encryption or decryption mechanism number over the data length. Before calling this function, ensure that the AES module is properly configured the key, data size, mode, etc. Only ECB, CBC, CTR, ICM, CFB, XTS and F8 operating modes should be used. The data is processed in 4-word (16-byte) blocks.

Definition at line 766 of file aes.c.

References AES_BASE, AESDataRead(), AESDataWrite(), AESLengthSet(), and ASSERT.

| bool AESDataProcessAuth | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src, | ||

| uint32_t * | pui32Dest, | ||

| uint32_t | ui32Length, | ||

| uint32_t * | pui32AuthSrc, | ||

| uint32_t | ui32AuthLength, | ||

| uint32_t * | pui32Tag | ||

| ) |

Processes and authenticates blocks of data, either encrypt it or decrypts it.

| ui32Base | is the base address of the AES module. |

| pui32Src | is a pointer to the memory location where the input data is stored. The data must be padded to the 16-byte boundary. |

| pui32Dest | is a pointer to the memory location output is written. The space for written data must be rounded up to the 16-byte boundary. |

| ui32Length | is the length of the cryptographic data in bytes. |

| pui32AuthSrc | is a pointer to the memory location where the additional authentication data is stored. The data must be padded to the 16-byte boundary. |

| ui32AuthLength | is the length of the additional authentication data in bytes. |

| pui32Tag | is a pointer to a 4-word array where the hash tag is written. |

This function encrypts or decrypts blocks of data in addition to authentication data. A hash tag is also produced. Before calling this function, ensure that the AES module is properly configured the key, data size, mode, etc. Only CCM and GCM modes should be used.

Definition at line 892 of file aes.c.

References AES_BASE, AESAuthLengthSet(), AESDataRead(), AESDataWrite(), AESLengthSet(), AESTagRead(), and ASSERT.

| void AESDataRead | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Dest | ||

| ) |

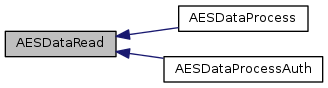

Reads plaintext/ciphertext from data registers with blocking.

| ui32Base | is the base address of the AES module. |

| pui32Dest | is a pointer to an array of words. |

This function reads a block of either plaintext or ciphertext out of the AES module. If the output is not ready, the function waits until it is ready. A block is 16 bytes or 4 words.

Definition at line 635 of file aes.c.

References AES_BASE, AES_CTRL_OUTPUT_READY, AES_O_CTRL, AES_O_DATA_IN_0, AES_O_DATA_IN_1, AES_O_DATA_IN_2, AES_O_DATA_IN_3, ASSERT, and HWREG.

Referenced by AESDataProcess(), and AESDataProcessAuth().

| bool AESDataReadNonBlocking | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Dest | ||

| ) |

Reads plaintext/ciphertext from data registers without blocking.

| ui32Base | is the base address of the AES module. |

| pui32Dest | is a pointer to an array of words of data. |

This function reads a block of either plaintext or ciphertext out of the AES module. If the output data is not ready, the function returns false. If the read completed successfully, the function returns true. A block is 16 bytes or 4 words.

Definition at line 590 of file aes.c.

References AES_BASE, AES_CTRL_OUTPUT_READY, AES_O_CTRL, AES_O_DATA_IN_0, AES_O_DATA_IN_1, AES_O_DATA_IN_2, AES_O_DATA_IN_3, ASSERT, and HWREG.

| void AESDataWrite | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

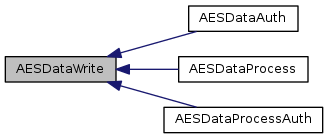

Writes plaintext/ciphertext to data registers with blocking.

| ui32Base | is the base address of the AES module. |

| pui32Src | is a pointer to an array of bytes. |

This function writes a block of either plaintext or ciphertext into the AES module. If the input is not ready, the function waits until it is ready before performing the write. A block is 16 bytes or 4 words.

Definition at line 718 of file aes.c.

References AES_BASE, AES_CTRL_INPUT_READY, AES_O_CTRL, AES_O_DATA_IN_0, AES_O_DATA_IN_1, AES_O_DATA_IN_2, AES_O_DATA_IN_3, ASSERT, and HWREG.

Referenced by AESDataAuth(), AESDataProcess(), and AESDataProcessAuth().

| bool AESDataWriteNonBlocking | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

Writes plaintext/ciphertext to data registers without blocking.

| ui32Base | is the base address of the AES module. |

| pui32Src | is a pointer to an array of words of data. |

This function writes a block of either plaintext or ciphertext into the AES module. If the input is not ready, the function returns false. If the write completed successfully, the function returns true. A block is 16 bytes or 4 words.

Definition at line 674 of file aes.c.

References AES_BASE, AES_CTRL_INPUT_READY, AES_O_CTRL, AES_O_DATA_IN_0, AES_O_DATA_IN_1, AES_O_DATA_IN_2, AES_O_DATA_IN_3, ASSERT, and HWREG.

| void AESDMADisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Flags | ||

| ) |

Disables uDMA requests for the AES module.

| ui32Base | is the base address of the AES module. |

| ui32Flags | is a bit mask of the uDMA requests to be disabled. |

This function disables the uDMA request sources in the AES module. The ui32Flags parameter is the logical OR of any of the following:

Definition at line 1283 of file aes.c.

References AES_BASE, AES_DMA_CONTEXT_IN, AES_DMA_CONTEXT_OUT, AES_DMA_DATA_IN, AES_DMA_DATA_OUT, AES_O_SYSCONFIG, ASSERT, and HWREG.

| void AESDMAEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Flags | ||

| ) |

Enables uDMA requests for the AES module.

| ui32Base | is the base address of the AES module. |

| ui32Flags | is a bit mask of the uDMA requests to be enabled. |

This function enables the uDMA request sources in the AES module. The ui32Flags parameter is the logical OR of any of the following:

Definition at line 1246 of file aes.c.

References AES_BASE, AES_DMA_CONTEXT_IN, AES_DMA_CONTEXT_OUT, AES_DMA_DATA_IN, AES_DMA_DATA_OUT, AES_O_SYSCONFIG, ASSERT, and HWREG.

| void AESIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears AES module interrupts.

| ui32Base | is the base address of the AES module. |

| ui32IntFlags | is a bit mask of the interrupt sources to disable. |

This function clears the interrupt sources in the AES module. The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1133 of file aes.c.

References AES_BASE, AES_INT_DMA_CONTEXT_IN, AES_INT_DMA_CONTEXT_OUT, AES_INT_DMA_DATA_IN, AES_INT_DMA_DATA_OUT, AES_O_DMAIC, ASSERT, and HWREG.

| void AESIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables AES module interrupts.

| ui32Base | is the base address of the AES module. |

| ui32IntFlags | is a bit mask of the interrupt sources to disable. |

This function disables the interrupt sources in the AES module. The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1086 of file aes.c.

References AES_BASE, AES_INT_CONTEXT_IN, AES_INT_CONTEXT_OUT, AES_INT_DATA_IN, AES_INT_DATA_OUT, AES_INT_DMA_CONTEXT_IN, AES_INT_DMA_CONTEXT_OUT, AES_INT_DMA_DATA_IN, AES_INT_DMA_DATA_OUT, AES_O_DMAIM, AES_O_IRQENABLE, ASSERT, and HWREG.

| void AESIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables AES module interrupts.

| ui32Base | is the base address of the AES module. |

| ui32IntFlags | is a bit mask of the interrupt sources to enable. |

This function enables the interrupts in the AES module. The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1035 of file aes.c.

References AES_BASE, AES_INT_CONTEXT_IN, AES_INT_CONTEXT_OUT, AES_INT_DATA_IN, AES_INT_DATA_OUT, AES_INT_DMA_CONTEXT_IN, AES_INT_DMA_CONTEXT_OUT, AES_INT_DMA_DATA_IN, AES_INT_DMA_DATA_OUT, AES_O_DMAIM, AES_O_IRQENABLE, ASSERT, and HWREG.

| void AESIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

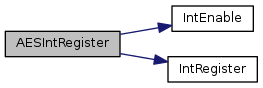

Registers an interrupt handler for the AES module.

| ui32Base | is the base address of the AES module. |

| pfnHandler | is a pointer to the function to be called when the enabled AES interrupts occur. |

This function registers the interrupt handler in the interrupt vector table, and enables AES interrupts on the interrupt controller; specific AES interrupt sources must be enabled using AESIntEnable(). The interrupt handler being registered must clear the source of the interrupt using AESIntClear().

If the application is using a static interrupt vector table stored in flash, then it is not necessary to register the interrupt handler this way. Instead, IntEnable() is used to enable AES interrupts on the interrupt controller.

Definition at line 1175 of file aes.c.

References AES_BASE, ASSERT, INT_AES0_TM4C129, IntEnable(), and IntRegister().

| uint32_t AESIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Returns the current AES module interrupt status.

| ui32Base | is the base address of the AES module. |

| bMasked | is false if the raw interrupt status is required and true if the masked interrupt status is required. |

Definition at line 976 of file aes.c.

References AES_BASE, AES_O_DMAMIS, AES_O_DMARIS, AES_O_IRQENABLE, AES_O_IRQSTATUS, ASSERT, and HWREG.

| void AESIntUnregister | ( | uint32_t | ui32Base | ) |

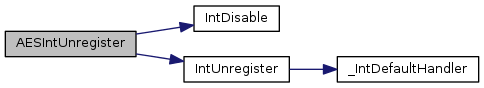

Unregisters an interrupt handler for the AES module.

| ui32Base | is the base address of the AES module. |

This function unregisters the previously registered interrupt handler and disables the interrupt in the interrupt controller.

Definition at line 1209 of file aes.c.

References AES_BASE, ASSERT, INT_AES0_TM4C129, IntDisable(), and IntUnregister().

| void AESIVRead | ( | uint32_t | ui32Base, |

| uint32_t * | pui32IVData | ||

| ) |

Saves the Initial Vector (IV) registers to a user-defined location.

| ui32Base | is the base address of the AES module. |

| pui32IVData | is pointer to the location that stores the IV data. |

This function stores the IV for use with authenticated encryption and decryption operations. It is assumed that the AES_CTRL_SAVE_CONTEXT bit is set in the AES_CTRL register.

Definition at line 439 of file aes.c.

References AES_BASE, AES_CTRL_SVCTXTRDY, AES_O_CTRL, AES_O_IV_IN_0, AES_O_IV_IN_1, AES_O_IV_IN_2, AES_O_IV_IN_3, ASSERT, and HWREG.

| void AESIVSet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32IVdata | ||

| ) |

Writes the Initial Vector (IV) register, needed in some of the AES Modes.

| ui32Base | is the base address of the AES module. |

| pui32IVdata | is an array of 4 words (128 bits), containing the IV value to be configured. The least significant word is in the 0th index. |

This functions writes the initial vector registers in the AES module.

Definition at line 408 of file aes.c.

References AES_BASE, AES_O_IV_IN_0, AES_O_IV_IN_1, AES_O_IV_IN_2, AES_O_IV_IN_3, ASSERT, and HWREG.

| void AESKey1Set | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Key, | ||

| uint32_t | ui32Keysize | ||

| ) |

Writes the key 1 configuration registers, which are used for encryption or decryption.

| ui32Base | is the base address for the AES module. |

| pui32Key | is an array of 32-bit words, containing the key to be configured. The least significant word in the 0th index. |

| ui32Keysize | is the size of the key, which must be one of the following values: AES_CFG_KEY_SIZE_128, AES_CFG_KEY_SIZE_192, or AES_CFG_KEY_SIZE_256. |

This function writes key 1 configuration registers based on the key size. This function is used in all modes.

Definition at line 269 of file aes.c.

References AES_BASE, AES_CFG_KEY_SIZE_128BIT, AES_CFG_KEY_SIZE_192BIT, AES_CFG_KEY_SIZE_256BIT, AES_O_KEY1_0, AES_O_KEY1_1, AES_O_KEY1_2, AES_O_KEY1_3, AES_O_KEY1_4, AES_O_KEY1_5, AES_O_KEY1_6, AES_O_KEY1_7, ASSERT, and HWREG.

| void AESKey2Set | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Key, | ||

| uint32_t | ui32Keysize | ||

| ) |

Writes the key 2 configuration registers, which are used for encryption or decryption.

| ui32Base | is the base address for the AES module. |

| pui32Key | is an array of 32-bit words, containing the key to be configured. The least significant word in the 0th index. |

| ui32Keysize | is the size of the key, which must be one of the following values: AES_CFG_KEY_SIZE_128, AES_CFG_KEY_SIZE_192, or AES_CFG_KEY_SIZE_256. |

This function writes the key 2 configuration registers based on the key size. This function is used in the F8, F9, XTS, CCM, and CBC-MAC modes.

Definition at line 325 of file aes.c.

References AES_BASE, AES_CFG_KEY_SIZE_128BIT, AES_CFG_KEY_SIZE_192BIT, AES_CFG_KEY_SIZE_256BIT, AES_O_KEY2_0, AES_O_KEY2_1, AES_O_KEY2_2, AES_O_KEY2_3, AES_O_KEY2_4, AES_O_KEY2_5, AES_O_KEY2_6, AES_O_KEY2_7, ASSERT, and HWREG.

| void AESKey3Set | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Key | ||

| ) |

Writes key 3 configuration registers, which are used for encryption or decryption.

| ui32Base | is the base address for the AES module. |

| pui32Key | is a pointer to an array of 4 words (128 bits), containing the key to be configured. The least significant word is in the 0th index. |

This function writes the key 2 configuration registers with key 3 data used in CBC-MAC and F8 modes. This key is always 128 bits.

Definition at line 378 of file aes.c.

References AES_BASE, AES_O_KEY2_4, AES_O_KEY2_5, AES_O_KEY2_6, AES_O_KEY2_7, ASSERT, and HWREG.

| void AESLengthSet | ( | uint32_t | ui32Base, |

| uint64_t | ui64Length | ||

| ) |

Used to set the write crypto data length in the AES module.

| ui32Base | is the base address of the AES module. |

| ui64Length | is the crypto data length in bytes. |

This function stores the cryptographic data length in blocks for all modes. Data lengths up to (2^61 - 1) bytes are allowed. For GCM, any value up to (2^36 - 2) bytes are allowed because a 32-bit block counter is used. For basic modes (ECB/CBC/CTR/ICM/CFB128), zero can be programmed into the length field, indicating that the length is infinite.

When this function is called, the engine is triggered to start using this context.

Definition at line 524 of file aes.c.

References AES_BASE, AES_O_C_LENGTH_0, AES_O_C_LENGTH_1, ASSERT, and HWREG.

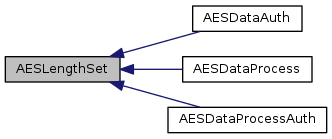

Referenced by AESDataAuth(), AESDataProcess(), and AESDataProcessAuth().

| void AESReset | ( | uint32_t | ui32Base | ) |

Resets the AES module.

| ui32Base | is the base address of the AES module. |

This function performs a softreset the AES module.

Definition at line 72 of file aes.c.

References AES_BASE, AES_O_SYSCONFIG, AES_O_SYSSTATUS, AES_SYSCONFIG_SOFTRESET, AES_SYSSTATUS_RESETDONE, ASSERT, and HWREG.

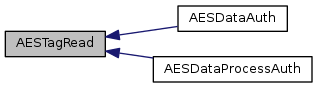

| void AESTagRead | ( | uint32_t | ui32Base, |

| uint32_t * | pui32TagData | ||

| ) |

Saves the tag registers to a user-defined location.

| ui32Base | is the base address of the AES module. |

| pui32TagData | is pointer to the location that stores the tag data. |

This function stores the tag data for use authenticated encryption and decryption operations. It is assumed that the AES_CTRL_SAVE_CONTEXT bit is set in the AES_CTRL register.

Definition at line 477 of file aes.c.

References AES_BASE, AES_CTRL_SVCTXTRDY, AES_O_CTRL, AES_O_TAG_OUT_0, AES_O_TAG_OUT_1, AES_O_TAG_OUT_2, AES_O_TAG_OUT_3, ASSERT, and HWREG.

Referenced by AESDataAuth(), and AESDataProcessAuth().