|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

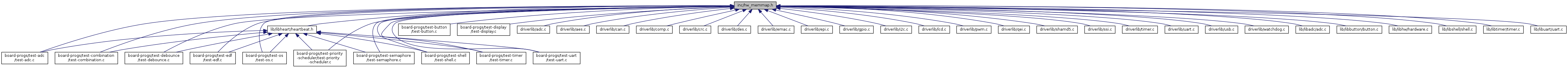

Go to the source code of this file.

Macros | |

| #define | FLASH_BASE 0x00000000 |

| #define | SRAM_BASE 0x20000000 |

| #define | WATCHDOG0_BASE 0x40000000 |

| #define | WATCHDOG1_BASE 0x40001000 |

| #define | GPIO_PORTA_BASE 0x40004000 |

| #define | GPIO_PORTB_BASE 0x40005000 |

| #define | GPIO_PORTC_BASE 0x40006000 |

| #define | GPIO_PORTD_BASE 0x40007000 |

| #define | SSI0_BASE 0x40008000 |

| #define | SSI1_BASE 0x40009000 |

| #define | SSI2_BASE 0x4000A000 |

| #define | SSI3_BASE 0x4000B000 |

| #define | UART0_BASE 0x4000C000 |

| #define | UART1_BASE 0x4000D000 |

| #define | UART2_BASE 0x4000E000 |

| #define | UART3_BASE 0x4000F000 |

| #define | UART4_BASE 0x40010000 |

| #define | UART5_BASE 0x40011000 |

| #define | UART6_BASE 0x40012000 |

| #define | UART7_BASE 0x40013000 |

| #define | I2C0_BASE 0x40020000 |

| #define | I2C1_BASE 0x40021000 |

| #define | I2C2_BASE 0x40022000 |

| #define | I2C3_BASE 0x40023000 |

| #define | GPIO_PORTE_BASE 0x40024000 |

| #define | GPIO_PORTF_BASE 0x40025000 |

| #define | GPIO_PORTG_BASE 0x40026000 |

| #define | GPIO_PORTH_BASE 0x40027000 |

| #define | PWM0_BASE 0x40028000 |

| #define | PWM1_BASE 0x40029000 |

| #define | QEI0_BASE 0x4002C000 |

| #define | QEI1_BASE 0x4002D000 |

| #define | TIMER0_BASE 0x40030000 |

| #define | TIMER1_BASE 0x40031000 |

| #define | TIMER2_BASE 0x40032000 |

| #define | TIMER3_BASE 0x40033000 |

| #define | TIMER4_BASE 0x40034000 |

| #define | TIMER5_BASE 0x40035000 |

| #define | WTIMER0_BASE 0x40036000 |

| #define | WTIMER1_BASE 0x40037000 |

| #define | ADC0_BASE 0x40038000 |

| #define | ADC1_BASE 0x40039000 |

| #define | COMP_BASE 0x4003C000 |

| #define | GPIO_PORTJ_BASE 0x4003D000 |

| #define | CAN0_BASE 0x40040000 |

| #define | CAN1_BASE 0x40041000 |

| #define | WTIMER2_BASE 0x4004C000 |

| #define | WTIMER3_BASE 0x4004D000 |

| #define | WTIMER4_BASE 0x4004E000 |

| #define | WTIMER5_BASE 0x4004F000 |

| #define | USB0_BASE 0x40050000 |

| #define | GPIO_PORTA_AHB_BASE 0x40058000 |

| #define | GPIO_PORTB_AHB_BASE 0x40059000 |

| #define | GPIO_PORTC_AHB_BASE 0x4005A000 |

| #define | GPIO_PORTD_AHB_BASE 0x4005B000 |

| #define | GPIO_PORTE_AHB_BASE 0x4005C000 |

| #define | GPIO_PORTF_AHB_BASE 0x4005D000 |

| #define | GPIO_PORTG_AHB_BASE 0x4005E000 |

| #define | GPIO_PORTH_AHB_BASE 0x4005F000 |

| #define | GPIO_PORTJ_AHB_BASE 0x40060000 |

| #define | GPIO_PORTK_BASE 0x40061000 |

| #define | GPIO_PORTL_BASE 0x40062000 |

| #define | GPIO_PORTM_BASE 0x40063000 |

| #define | GPIO_PORTN_BASE 0x40064000 |

| #define | GPIO_PORTP_BASE 0x40065000 |

| #define | GPIO_PORTQ_BASE 0x40066000 |

| #define | GPIO_PORTR_BASE 0x40067000 |

| #define | GPIO_PORTS_BASE 0x40068000 |

| #define | GPIO_PORTT_BASE 0x40069000 |

| #define | EEPROM_BASE 0x400AF000 |

| #define | ONEWIRE0_BASE 0x400B6000 |

| #define | I2C8_BASE 0x400B8000 |

| #define | I2C9_BASE 0x400B9000 |

| #define | I2C4_BASE 0x400C0000 |

| #define | I2C5_BASE 0x400C1000 |

| #define | I2C6_BASE 0x400C2000 |

| #define | I2C7_BASE 0x400C3000 |

| #define | EPI0_BASE 0x400D0000 |

| #define | TIMER6_BASE 0x400E0000 |

| #define | TIMER7_BASE 0x400E1000 |

| #define | EMAC0_BASE 0x400EC000 |

| #define | SYSEXC_BASE 0x400F9000 |

| #define | HIB_BASE 0x400FC000 |

| #define | FLASH_CTRL_BASE 0x400FD000 |

| #define | SYSCTL_BASE 0x400FE000 |

| #define | UDMA_BASE 0x400FF000 |

| #define | CCM0_BASE 0x44030000 |

| #define | SHAMD5_BASE 0x44034000 |

| #define | AES_BASE 0x44036000 |

| #define | DES_BASE 0x44038000 |

| #define | LCD0_BASE 0x44050000 |

| #define | ITM_BASE 0xE0000000 |

| #define | DWT_BASE 0xE0001000 |

| #define | FPB_BASE 0xE0002000 |

| #define | NVIC_BASE 0xE000E000 |

| #define | TPIU_BASE 0xE0040000 |

| #define ADC0_BASE 0x40038000 |

Definition at line 89 of file hw_memmap.h.

Referenced by _ADCIntNumberGet(), ADC0Seq0_Handler(), ADC0Seq1_Handler(), ADC0Seq2_Handler(), ADC0Seq3_Handler(), adc_init(), ADCBusy(), ADCClockConfigGet(), ADCClockConfigSet(), ADCComparatorConfigure(), ADCComparatorIntClear(), ADCComparatorIntDisable(), ADCComparatorIntEnable(), ADCComparatorIntStatus(), ADCComparatorRegionSet(), ADCComparatorReset(), ADCHardwareOversampleConfigure(), ADCIntClear(), ADCIntDisable(), ADCIntDisableEx(), ADCIntEnable(), ADCIntEnableEx(), ADCIntRegister(), ADCIntStatus(), ADCIntStatusEx(), ADCIntUnregister(), ADCPhaseDelayGet(), ADCPhaseDelaySet(), ADCProcessorTrigger(), ADCReferenceGet(), ADCReferenceSet(), ADCSequenceConfigure(), ADCSequenceDataGet(), ADCSequenceDisable(), ADCSequenceDMADisable(), ADCSequenceDMAEnable(), ADCSequenceEnable(), ADCSequenceOverflow(), ADCSequenceOverflowClear(), ADCSequenceStepConfigure(), ADCSequenceUnderflow(), ADCSequenceUnderflowClear(), ADCSoftwareOversampleConfigure(), ADCSoftwareOversampleDataGet(), ADCSoftwareOversampleStepConfigure(), and main().

| #define ADC1_BASE 0x40039000 |

Definition at line 90 of file hw_memmap.h.

Referenced by ADCBusy(), ADCComparatorConfigure(), ADCComparatorIntClear(), ADCComparatorIntDisable(), ADCComparatorIntEnable(), ADCComparatorIntStatus(), ADCComparatorRegionSet(), ADCComparatorReset(), ADCHardwareOversampleConfigure(), ADCIntClear(), ADCIntDisable(), ADCIntDisableEx(), ADCIntEnable(), ADCIntEnableEx(), ADCIntRegister(), ADCIntStatus(), ADCIntStatusEx(), ADCIntUnregister(), ADCPhaseDelayGet(), ADCPhaseDelaySet(), ADCProcessorTrigger(), ADCReferenceGet(), ADCReferenceSet(), ADCSequenceConfigure(), ADCSequenceDataGet(), ADCSequenceDisable(), ADCSequenceDMADisable(), ADCSequenceDMAEnable(), ADCSequenceEnable(), ADCSequenceOverflow(), ADCSequenceOverflowClear(), ADCSequenceStepConfigure(), ADCSequenceUnderflow(), ADCSequenceUnderflowClear(), ADCSoftwareOversampleConfigure(), ADCSoftwareOversampleDataGet(), and ADCSoftwareOversampleStepConfigure().

| #define AES_BASE 0x44036000 |

Definition at line 140 of file hw_memmap.h.

Referenced by AESAuthLengthSet(), AESConfigSet(), AESDataAuth(), AESDataProcess(), AESDataProcessAuth(), AESDataRead(), AESDataReadNonBlocking(), AESDataWrite(), AESDataWriteNonBlocking(), AESDMADisable(), AESDMAEnable(), AESIntClear(), AESIntDisable(), AESIntEnable(), AESIntRegister(), AESIntStatus(), AESIntUnregister(), AESIVRead(), AESIVSet(), AESKey1Set(), AESKey2Set(), AESKey3Set(), AESLengthSet(), AESReset(), and AESTagRead().

| #define CAN0_BASE 0x40040000 |

Definition at line 93 of file hw_memmap.h.

Referenced by _CANIntNumberGet().

| #define CAN1_BASE 0x40041000 |

Definition at line 94 of file hw_memmap.h.

Referenced by _CANIntNumberGet().

| #define CCM0_BASE 0x44030000 |

Definition at line 138 of file hw_memmap.h.

Referenced by CRCConfigSet(), CRCDataProcess(), CRCDataWrite(), CRCResultRead(), and CRCSeedSet().

| #define COMP_BASE 0x4003C000 |

Definition at line 91 of file hw_memmap.h.

Referenced by ComparatorConfigure(), ComparatorIntClear(), ComparatorIntDisable(), ComparatorIntEnable(), ComparatorIntRegister(), ComparatorIntStatus(), ComparatorIntUnregister(), ComparatorRefSet(), and ComparatorValueGet().

| #define DES_BASE 0x44038000 |

Definition at line 142 of file hw_memmap.h.

Referenced by DESConfigSet(), DESDataProcess(), DESDataRead(), DESDataReadNonBlocking(), DESDataWrite(), DESDataWriteNonBlocking(), DESDMADisable(), DESDMAEnable(), DESIntClear(), DESIntDisable(), DESIntEnable(), DESIntRegister(), DESIntStatus(), DESIntUnregister(), DESIVSet(), DESKeySet(), DESLengthSet(), and DESReset().

| #define DWT_BASE 0xE0001000 |

Definition at line 146 of file hw_memmap.h.

| #define EEPROM_BASE 0x400AF000 |

Definition at line 121 of file hw_memmap.h.

| #define EMAC0_BASE 0x400EC000 |

Definition at line 132 of file hw_memmap.h.

Referenced by EMACInit(), EMACIntClear(), EMACIntDisable(), EMACIntStatus(), EMACPHYConfigSet(), EMACPHYExtendedRead(), EMACPHYExtendedWrite(), EMACPHYRead(), EMACPHYWrite(), EMACPowerManagementControlGet(), EMACPowerManagementControlSet(), EMACPowerManagementStatusGet(), EMACRemoteWakeUpFrameFilterGet(), EMACRemoteWakeUpFrameFilterSet(), EMACTimestampAddendSet(), EMACTimestampConfigGet(), EMACTimestampConfigSet(), EMACTimestampDisable(), EMACTimestampEnable(), EMACTimestampIntStatus(), EMACTimestampPPSCommand(), EMACTimestampPPSCommandModeSet(), EMACTimestampPPSPeriodSet(), EMACTimestampPPSSimpleModeSet(), EMACTimestampSysTimeGet(), EMACTimestampSysTimeSet(), EMACTimestampSysTimeUpdate(), EMACTimestampTargetIntDisable(), EMACTimestampTargetIntEnable(), EMACTimestampTargetSet(), EMACVLANHashFilterGet(), EMACVLANHashFilterSet(), EMACVLANRxConfigGet(), EMACVLANRxConfigSet(), EMACVLANTxConfigGet(), and EMACVLANTxConfigSet().

| #define EPI0_BASE 0x400D0000 |

Definition at line 129 of file hw_memmap.h.

Referenced by _EPIIntNumberGet(), EPIAddressMapSet(), EPIConfigGPModeSet(), EPIConfigHB16CSSet(), EPIConfigHB16Set(), EPIConfigHB16TimingSet(), EPIConfigHB8CSSet(), EPIConfigHB8Set(), EPIConfigHB8TimingSet(), EPIConfigSDRAMSet(), EPIDividerCSSet(), EPIDividerSet(), EPIDMATxCount(), EPIFIFOConfig(), EPIIntDisable(), EPIIntEnable(), EPIIntErrorClear(), EPIIntErrorStatus(), EPIIntRegister(), EPIIntStatus(), EPIIntUnregister(), EPIModeSet(), EPINonBlockingReadAvail(), EPINonBlockingReadConfigure(), EPINonBlockingReadCount(), EPINonBlockingReadGet16(), EPINonBlockingReadGet32(), EPINonBlockingReadGet8(), EPINonBlockingReadStart(), EPINonBlockingReadStop(), EPIPSRAMConfigRegGet(), EPIPSRAMConfigRegGetNonBlocking(), EPIPSRAMConfigRegRead(), EPIPSRAMConfigRegSet(), and EPIWriteFIFOCountGet().

| #define FLASH_BASE 0x00000000 |

Definition at line 49 of file hw_memmap.h.

| #define FLASH_CTRL_BASE 0x400FD000 |

Definition at line 135 of file hw_memmap.h.

| #define FPB_BASE 0xE0002000 |

Definition at line 147 of file hw_memmap.h.

| #define GPIO_PORTA_AHB_BASE 0x40058000 |

Definition at line 100 of file hw_memmap.h.

| #define GPIO_PORTA_BASE 0x40004000 |

Definition at line 53 of file hw_memmap.h.

Referenced by main(), and uart_init().

| #define GPIO_PORTB_AHB_BASE 0x40059000 |

Definition at line 101 of file hw_memmap.h.

| #define GPIO_PORTB_BASE 0x40005000 |

Definition at line 54 of file hw_memmap.h.

| #define GPIO_PORTC_AHB_BASE 0x4005A000 |

Definition at line 102 of file hw_memmap.h.

| #define GPIO_PORTC_BASE 0x40006000 |

Definition at line 55 of file hw_memmap.h.

| #define GPIO_PORTD_AHB_BASE 0x4005B000 |

Definition at line 103 of file hw_memmap.h.

| #define GPIO_PORTD_BASE 0x40007000 |

Definition at line 56 of file hw_memmap.h.

| #define GPIO_PORTE_AHB_BASE 0x4005C000 |

Definition at line 104 of file hw_memmap.h.

Referenced by adc_init().

| #define GPIO_PORTE_BASE 0x40024000 |

Definition at line 73 of file hw_memmap.h.

Referenced by _hw_get_channel().

| #define GPIO_PORTF_AHB_BASE 0x4005D000 |

Definition at line 105 of file hw_memmap.h.

| #define GPIO_PORTF_BASE 0x40025000 |

Definition at line 74 of file hw_memmap.h.

Referenced by button_debounce_end(), button_debounce_start(), button_init(), GPIOPortF_Handler(), led_blink_blue(), led_blink_green(), led_blink_red(), led_single_blink_blue(), led_single_blink_green(), led_single_blink_red(), main(), postpone_suicide(), Thread1(), Thread2(), and uart_consumer().

| #define GPIO_PORTG_AHB_BASE 0x4005E000 |

Definition at line 106 of file hw_memmap.h.

| #define GPIO_PORTG_BASE 0x40026000 |

Definition at line 75 of file hw_memmap.h.

| #define GPIO_PORTH_AHB_BASE 0x4005F000 |

Definition at line 107 of file hw_memmap.h.

| #define GPIO_PORTH_BASE 0x40027000 |

Definition at line 76 of file hw_memmap.h.

| #define GPIO_PORTJ_AHB_BASE 0x40060000 |

Definition at line 108 of file hw_memmap.h.

| #define GPIO_PORTJ_BASE 0x4003D000 |

Definition at line 92 of file hw_memmap.h.

| #define GPIO_PORTK_BASE 0x40061000 |

Definition at line 109 of file hw_memmap.h.

| #define GPIO_PORTL_BASE 0x40062000 |

Definition at line 110 of file hw_memmap.h.

| #define GPIO_PORTM_BASE 0x40063000 |

Definition at line 111 of file hw_memmap.h.

| #define GPIO_PORTN_BASE 0x40064000 |

Definition at line 112 of file hw_memmap.h.

| #define GPIO_PORTP_BASE 0x40065000 |

Definition at line 113 of file hw_memmap.h.

| #define GPIO_PORTQ_BASE 0x40066000 |

Definition at line 114 of file hw_memmap.h.

| #define GPIO_PORTR_BASE 0x40067000 |

Definition at line 115 of file hw_memmap.h.

| #define GPIO_PORTS_BASE 0x40068000 |

Definition at line 117 of file hw_memmap.h.

| #define GPIO_PORTT_BASE 0x40069000 |

Definition at line 119 of file hw_memmap.h.

| #define HIB_BASE 0x400FC000 |

Definition at line 134 of file hw_memmap.h.

| #define I2C0_BASE 0x40020000 |

Definition at line 69 of file hw_memmap.h.

| #define I2C1_BASE 0x40021000 |

Definition at line 70 of file hw_memmap.h.

| #define I2C2_BASE 0x40022000 |

Definition at line 71 of file hw_memmap.h.

| #define I2C3_BASE 0x40023000 |

Definition at line 72 of file hw_memmap.h.

| #define I2C4_BASE 0x400C0000 |

Definition at line 125 of file hw_memmap.h.

| #define I2C5_BASE 0x400C1000 |

Definition at line 126 of file hw_memmap.h.

| #define I2C6_BASE 0x400C2000 |

Definition at line 127 of file hw_memmap.h.

| #define I2C7_BASE 0x400C3000 |

Definition at line 128 of file hw_memmap.h.

| #define I2C8_BASE 0x400B8000 |

Definition at line 123 of file hw_memmap.h.

| #define I2C9_BASE 0x400B9000 |

Definition at line 124 of file hw_memmap.h.

| #define ITM_BASE 0xE0000000 |

Definition at line 145 of file hw_memmap.h.

| #define LCD0_BASE 0x44050000 |

Definition at line 144 of file hw_memmap.h.

Referenced by LCDClockReset(), LCDDMAConfigSet(), LCDIDDCommandWrite(), LCDIDDConfigSet(), LCDIDDDataRead(), LCDIDDDataWrite(), LCDIDDDMADisable(), LCDIDDDMAWrite(), LCDIDDIndexedRead(), LCDIDDIndexedWrite(), LCDIDDStatusRead(), LCDIDDTimingSet(), LCDIntClear(), LCDIntDisable(), LCDIntEnable(), LCDIntRegister(), LCDIntStatus(), LCDIntUnregister(), LCDModeSet(), LCDRasterACBiasIntCountSet(), LCDRasterConfigSet(), LCDRasterDisable(), LCDRasterEnable(), LCDRasterEnabled(), LCDRasterFrameBufferSet(), LCDRasterPaletteSet(), LCDRasterSubPanelConfigSet(), LCDRasterSubPanelDisable(), LCDRasterSubPanelEnable(), and LCDRasterTimingSet().

| #define NVIC_BASE 0xE000E000 |

Definition at line 148 of file hw_memmap.h.

| #define ONEWIRE0_BASE 0x400B6000 |

Definition at line 122 of file hw_memmap.h.

| #define PWM0_BASE 0x40028000 |

Definition at line 77 of file hw_memmap.h.

Referenced by _PWMFaultIntNumberGet(), _PWMGenIntNumberGet(), PWMClockGet(), PWMClockSet(), PWMDeadBandDisable(), PWMDeadBandEnable(), PWMFaultIntClear(), PWMFaultIntClearExt(), PWMFaultIntRegister(), PWMFaultIntUnregister(), PWMGenConfigure(), PWMGenDisable(), PWMGenEnable(), PWMGenFaultClear(), PWMGenFaultConfigure(), PWMGenFaultStatus(), PWMGenFaultTriggerGet(), PWMGenFaultTriggerSet(), PWMGenIntClear(), PWMGenIntRegister(), PWMGenIntStatus(), PWMGenIntTrigDisable(), PWMGenIntTrigEnable(), PWMGenIntUnregister(), PWMGenPeriodGet(), PWMGenPeriodSet(), PWMIntDisable(), PWMIntEnable(), PWMIntStatus(), PWMOutputFault(), PWMOutputFaultLevel(), PWMOutputInvert(), PWMOutputState(), PWMOutputUpdateMode(), PWMPulseWidthGet(), PWMPulseWidthSet(), PWMSyncTimeBase(), and PWMSyncUpdate().

| #define PWM1_BASE 0x40029000 |

Definition at line 78 of file hw_memmap.h.

Referenced by _PWMGenIntNumberGet(), PWMClockGet(), PWMClockSet(), PWMDeadBandDisable(), PWMDeadBandEnable(), PWMFaultIntClear(), PWMFaultIntClearExt(), PWMFaultIntRegister(), PWMFaultIntUnregister(), PWMGenConfigure(), PWMGenDisable(), PWMGenEnable(), PWMGenFaultClear(), PWMGenFaultConfigure(), PWMGenFaultStatus(), PWMGenFaultTriggerGet(), PWMGenFaultTriggerSet(), PWMGenIntClear(), PWMGenIntRegister(), PWMGenIntStatus(), PWMGenIntTrigDisable(), PWMGenIntTrigEnable(), PWMGenIntUnregister(), PWMGenPeriodGet(), PWMGenPeriodSet(), PWMIntDisable(), PWMIntEnable(), PWMIntStatus(), PWMOutputFault(), PWMOutputFaultLevel(), PWMOutputInvert(), PWMOutputState(), PWMOutputUpdateMode(), PWMPulseWidthGet(), PWMPulseWidthSet(), PWMSyncTimeBase(), and PWMSyncUpdate().

| #define QEI0_BASE 0x4002C000 |

Definition at line 79 of file hw_memmap.h.

Referenced by _QEIIntNumberGet(), QEIConfigure(), QEIDirectionGet(), QEIDisable(), QEIEnable(), QEIErrorGet(), QEIIntClear(), QEIIntDisable(), QEIIntEnable(), QEIIntRegister(), QEIIntStatus(), QEIIntUnregister(), QEIPositionGet(), QEIPositionSet(), QEIVelocityConfigure(), QEIVelocityDisable(), QEIVelocityEnable(), and QEIVelocityGet().

| #define QEI1_BASE 0x4002D000 |

Definition at line 80 of file hw_memmap.h.

Referenced by _QEIIntNumberGet(), QEIConfigure(), QEIDirectionGet(), QEIDisable(), QEIEnable(), QEIErrorGet(), QEIIntClear(), QEIIntDisable(), QEIIntEnable(), QEIIntRegister(), QEIIntStatus(), QEIIntUnregister(), QEIPositionGet(), QEIPositionSet(), QEIVelocityConfigure(), QEIVelocityDisable(), QEIVelocityEnable(), and QEIVelocityGet().

| #define SHAMD5_BASE 0x44034000 |

Definition at line 139 of file hw_memmap.h.

Referenced by _SHAMD5DataWriteMultiple(), SHAMD5ConfigSet(), SHAMD5DataProcess(), SHAMD5DataWrite(), SHAMD5DataWriteNonBlocking(), SHAMD5DMADisable(), SHAMD5DMAEnable(), SHAMD5HashLengthSet(), SHAMD5HMACKeySet(), SHAMD5HMACPPKeyGenerate(), SHAMD5HMACPPKeySet(), SHAMD5HMACProcess(), SHAMD5IntClear(), SHAMD5IntDisable(), SHAMD5IntEnable(), SHAMD5IntRegister(), SHAMD5IntStatus(), SHAMD5IntUnregister(), SHAMD5Reset(), and SHAMD5ResultRead().

| #define SRAM_BASE 0x20000000 |

Definition at line 50 of file hw_memmap.h.

| #define SSI0_BASE 0x40008000 |

Definition at line 57 of file hw_memmap.h.

| #define SSI1_BASE 0x40009000 |

Definition at line 58 of file hw_memmap.h.

| #define SSI2_BASE 0x4000A000 |

Definition at line 59 of file hw_memmap.h.

| #define SSI3_BASE 0x4000B000 |

Definition at line 60 of file hw_memmap.h.

| #define SYSCTL_BASE 0x400FE000 |

Definition at line 136 of file hw_memmap.h.

| #define SYSEXC_BASE 0x400F9000 |

Definition at line 133 of file hw_memmap.h.

| #define TIMER0_BASE 0x40030000 |

Definition at line 81 of file hw_memmap.h.

Referenced by _hw_get_channel(), button_debounce_start(), hw_driver_init(), main(), TIMER0A_Handler(), timer_task(), and TimerSynchronize().

| #define TIMER1_BASE 0x40031000 |

Definition at line 82 of file hw_memmap.h.

Referenced by main(), and TIMER1A_Handler().

| #define TIMER2_BASE 0x40032000 |

Definition at line 83 of file hw_memmap.h.

Referenced by TIMER2A_Handler().

| #define TIMER3_BASE 0x40033000 |

Definition at line 84 of file hw_memmap.h.

| #define TIMER4_BASE 0x40034000 |

Definition at line 85 of file hw_memmap.h.

| #define TIMER5_BASE 0x40035000 |

Definition at line 86 of file hw_memmap.h.

| #define TIMER6_BASE 0x400E0000 |

Definition at line 130 of file hw_memmap.h.

| #define TIMER7_BASE 0x400E1000 |

Definition at line 131 of file hw_memmap.h.

| #define TPIU_BASE 0xE0040000 |

Definition at line 149 of file hw_memmap.h.

| #define UART0_BASE 0x4000C000 |

Definition at line 61 of file hw_memmap.h.

Referenced by _hw_get_channel(), doctor(), hw_daemon(), hw_driver_init(), main(), shell_kill(), shell_spawn(), UART0_Handler(), and uart_consumer().

| #define UART1_BASE 0x4000D000 |

Definition at line 62 of file hw_memmap.h.

Referenced by UARTModemControlClear(), UARTModemControlGet(), UARTModemControlSet(), and UARTModemStatusGet().

| #define UART2_BASE 0x4000E000 |

Definition at line 63 of file hw_memmap.h.

| #define UART3_BASE 0x4000F000 |

Definition at line 64 of file hw_memmap.h.

| #define UART4_BASE 0x40010000 |

Definition at line 65 of file hw_memmap.h.

| #define UART5_BASE 0x40011000 |

Definition at line 66 of file hw_memmap.h.

| #define UART6_BASE 0x40012000 |

Definition at line 67 of file hw_memmap.h.

| #define UART7_BASE 0x40013000 |

Definition at line 68 of file hw_memmap.h.

| #define UDMA_BASE 0x400FF000 |

Definition at line 137 of file hw_memmap.h.

| #define USB0_BASE 0x40050000 |

Definition at line 99 of file hw_memmap.h.

Referenced by _USBIndexRead(), _USBIndexWrite(), USBClockDisable(), USBClockEnable(), USBDevAddrGet(), USBDevAddrSet(), USBDevConnect(), USBDevDisconnect(), USBDevEndpointConfigGet(), USBDevEndpointConfigSet(), USBDevEndpointDataAck(), USBDevEndpointStall(), USBDevEndpointStallClear(), USBDevEndpointStatusClear(), USBDevLPMConfig(), USBDevLPMDisable(), USBDevLPMEnable(), USBDevLPMRemoteWake(), USBDevMode(), USBDevSpeedGet(), USBDMAChannelAddressGet(), USBDMAChannelAddressSet(), USBDMAChannelConfigSet(), USBDMAChannelCountGet(), USBDMAChannelCountSet(), USBDMAChannelDisable(), USBDMAChannelEnable(), USBDMAChannelIntDisable(), USBDMAChannelIntEnable(), USBDMAChannelIntStatus(), USBDMAChannelStatus(), USBDMAChannelStatusClear(), USBDMANumChannels(), USBEndpointDataAvail(), USBEndpointDataGet(), USBEndpointDataPut(), USBEndpointDataSend(), USBEndpointDataToggleClear(), USBEndpointDMAChannel(), USBEndpointStatus(), USBFIFOConfigGet(), USBFIFOConfigSet(), USBFIFOFlush(), USBFrameNumberGet(), USBHighSpeed(), USBHostAddrGet(), USBHostAddrSet(), USBHostEndpointConfig(), USBHostEndpointDataAck(), USBHostEndpointDataToggle(), USBHostEndpointPing(), USBHostEndpointSpeed(), USBHostEndpointStatusClear(), USBHostHubAddrGet(), USBHostHubAddrSet(), USBHostLPMConfig(), USBHostLPMResume(), USBHostLPMSend(), USBHostMode(), USBHostPwrConfig(), USBHostPwrDisable(), USBHostPwrEnable(), USBHostPwrFaultDisable(), USBHostPwrFaultEnable(), USBHostRequestIN(), USBHostRequestINClear(), USBHostRequestStatus(), USBHostReset(), USBHostResume(), USBHostSpeedGet(), USBHostSuspend(), USBIntDisableControl(), USBIntDisableEndpoint(), USBIntEnableControl(), USBIntEnableEndpoint(), USBIntRegister(), USBIntStatusControl(), USBIntStatusEndpoint(), USBIntUnregister(), USBLPMEndpointGet(), USBLPMIntDisable(), USBLPMIntEnable(), USBLPMIntStatus(), USBLPMLinkStateGet(), USBLPMRemoteWakeEnabled(), USBModeConfig(), USBModeGet(), USBOTGMode(), USBOTGSessionRequest(), USBULPIRegRead(), and USBULPIRegWrite().

| #define WATCHDOG0_BASE 0x40000000 |

Definition at line 51 of file hw_memmap.h.

Referenced by WatchdogEnable(), WatchdogIntClear(), WatchdogIntEnable(), WatchdogIntRegister(), WatchdogIntStatus(), WatchdogIntTypeSet(), WatchdogIntUnregister(), WatchdogLock(), WatchdogLockState(), WatchdogReloadGet(), WatchdogReloadSet(), WatchdogResetDisable(), WatchdogResetEnable(), WatchdogRunning(), WatchdogStallDisable(), WatchdogStallEnable(), WatchdogUnlock(), and WatchdogValueGet().

| #define WATCHDOG1_BASE 0x40001000 |

Definition at line 52 of file hw_memmap.h.

Referenced by WatchdogEnable(), WatchdogIntClear(), WatchdogIntEnable(), WatchdogIntRegister(), WatchdogIntStatus(), WatchdogIntTypeSet(), WatchdogIntUnregister(), WatchdogLock(), WatchdogLockState(), WatchdogReloadGet(), WatchdogReloadSet(), WatchdogResetDisable(), WatchdogResetEnable(), WatchdogRunning(), WatchdogStallDisable(), WatchdogStallEnable(), WatchdogUnlock(), and WatchdogValueGet().

| #define WTIMER0_BASE 0x40036000 |

Definition at line 87 of file hw_memmap.h.

| #define WTIMER1_BASE 0x40037000 |

Definition at line 88 of file hw_memmap.h.

| #define WTIMER2_BASE 0x4004C000 |

Definition at line 95 of file hw_memmap.h.

| #define WTIMER3_BASE 0x4004D000 |

Definition at line 96 of file hw_memmap.h.

| #define WTIMER4_BASE 0x4004E000 |

Definition at line 97 of file hw_memmap.h.

| #define WTIMER5_BASE 0x4004F000 |

Definition at line 98 of file hw_memmap.h.