|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Functions | |

| void | SHAMD5Reset (uint32_t ui32Base) |

| void | SHAMD5DMAEnable (uint32_t ui32Base) |

| void | SHAMD5DMADisable (uint32_t ui32Base) |

| uint32_t | SHAMD5IntStatus (uint32_t ui32Base, bool bMasked) |

| void | SHAMD5IntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | SHAMD5IntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | SHAMD5IntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | SHAMD5IntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | SHAMD5IntUnregister (uint32_t ui32Base) |

| void | SHAMD5HashLengthSet (uint32_t ui32Base, uint32_t ui32Length) |

| void | SHAMD5ConfigSet (uint32_t ui32Base, uint32_t ui32Mode) |

| bool | SHAMD5DataWriteNonBlocking (uint32_t ui32Base, uint32_t *pui32Src) |

| void | SHAMD5DataWrite (uint32_t ui32Base, uint32_t *pui32Src) |

| void | SHAMD5ResultRead (uint32_t ui32Base, uint32_t *pui32Dest) |

| static void | _SHAMD5DataWriteMultiple (uint32_t ui32Base, uint32_t *pui32DataSrc, uint32_t ui32DataLength) |

| void | SHAMD5DataProcess (uint32_t ui32Base, uint32_t *pui32DataSrc, uint32_t ui32DataLength, uint32_t *pui32HashResult) |

| void | SHAMD5HMACProcess (uint32_t ui32Base, uint32_t *pui32DataSrc, uint32_t ui32DataLength, uint32_t *pui32HashResult) |

| void | SHAMD5HMACPPKeyGenerate (uint32_t ui32Base, uint32_t *pui32Key, uint32_t *pui32PPKey) |

| void | SHAMD5HMACKeySet (uint32_t ui32Base, uint32_t *pui32Src) |

| void | SHAMD5HMACPPKeySet (uint32_t ui32Base, uint32_t *pui32Src) |

|

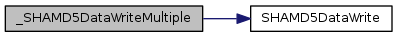

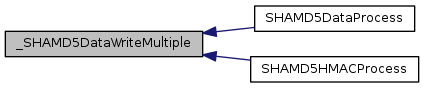

static |

Writes multiple words of data into the SHA/MD5 data registers.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32DataSrc | is a pointer to an array of data to be written. |

| ui32DataLength | is the length of the data to be written in bytes. |

This function writes a variable number of words into the SHA/MD5 data registers. The function waits for each block of data to be processed before another is written. The ui32DataLength parameter must be a multiple of 4 to fall on a word boundry.

Definition at line 712 of file shamd5.c.

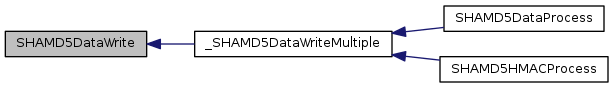

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_INPUT_READY, SHAMD5_O_DATA_0_IN, SHAMD5_O_IRQSTATUS, and SHAMD5DataWrite().

Referenced by SHAMD5DataProcess(), and SHAMD5HMACProcess().

| void SHAMD5ConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Mode | ||

| ) |

Writes the mode in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| ui32Mode | is the mode of the SHA/MD5 module. |

This function writes the mode register configuring the SHA/MD5 module.

The ui32Mode parameter is a bit-wise OR of values:

Definition at line 469 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_ALGO_HMAC_MD5, SHAMD5_ALGO_HMAC_SHA1, SHAMD5_ALGO_HMAC_SHA224, SHAMD5_ALGO_HMAC_SHA256, SHAMD5_ALGO_MD5, SHAMD5_ALGO_SHA1, SHAMD5_ALGO_SHA224, SHAMD5_ALGO_SHA256, SHAMD5_BASE, and SHAMD5_O_MODE.

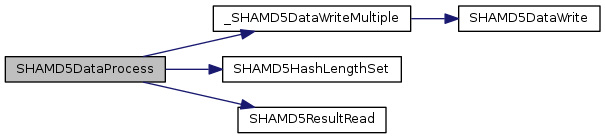

| void SHAMD5DataProcess | ( | uint32_t | ui32Base, |

| uint32_t * | pui32DataSrc, | ||

| uint32_t | ui32DataLength, | ||

| uint32_t * | pui32HashResult | ||

| ) |

Compute a hash using the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32DataSrc | is a pointer to an array of data that contains the data that will be hashed. |

| ui32DataLength | specifies the length of the data to be hashed in bytes. |

| pui32HashResult | is a pointer to an array that holds the result of the hashing operation. |

This function computes the hash of an array of data using the SHA/MD5 module.

The length of the hash result is dependent on the algorithm that is in use. The following table shows the correct array size for each algorithm:

| MD5 | 4 Words (128 bits) | | SHA-1 | 5 Words (160 bits) | | SHA-224 | 7 Words (224 bits) |

Definition at line 808 of file shamd5.c.

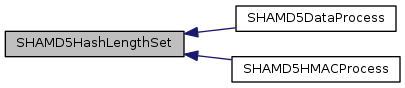

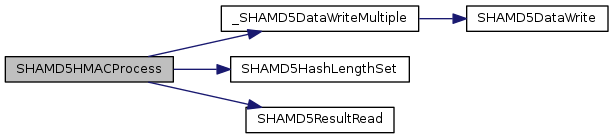

References _SHAMD5DataWriteMultiple(), ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_O_IRQSTATUS, SHAMD5HashLengthSet(), and SHAMD5ResultRead().

| void SHAMD5DataWrite | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

Perform a blocking write of 16 words of data to the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Src | is the pointer to the 16-word array of data that will be written. |

This function does not return until the module is ready to accept data and the data has been written.

Definition at line 552 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_INPUT_READY, SHAMD5_O_DATA_0_IN, and SHAMD5_O_IRQSTATUS.

Referenced by _SHAMD5DataWriteMultiple().

| bool SHAMD5DataWriteNonBlocking | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

Perform a non-blocking write of 16 words of data to the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Src | is the pointer to the 16-word array of data that will be written. |

This function writes 16 words of data into the data register regardless of whether or not the module is ready to accept the data.

Definition at line 506 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_INPUT_READY, SHAMD5_O_DATA_0_IN, and SHAMD5_O_IRQSTATUS.

| void SHAMD5DMADisable | ( | uint32_t | ui32Base | ) |

Disables the uDMA requests in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

This function configures the DMA options of the SHA/MD5 module.

Definition at line 137 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_O_SYSCONFIG, SHAMD5_SYSCONFIG_DMA_EN, and SHAMD5_SYSCONFIG_SADVANCED.

| void SHAMD5DMAEnable | ( | uint32_t | ui32Base | ) |

Enables the uDMA requests in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

This function configures the DMA options of the SHA/MD5 module.

Definition at line 111 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_O_SYSCONFIG, SHAMD5_SYSCONFIG_DMA_EN, and SHAMD5_SYSCONFIG_SADVANCED.

| void SHAMD5HashLengthSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Length | ||

| ) |

Write the hash length to the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| ui32Length | is the hash length in bytes. |

This function writes the length of the hash data of the current operation to the SHA/MD5 module. The value must be a multiple of 64 if the close hash is not set in the mode register.

Definition at line 432 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, and SHAMD5_O_LENGTH.

Referenced by SHAMD5DataProcess(), and SHAMD5HMACProcess().

| void SHAMD5HMACKeySet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

Writes an HMAC key to the digest registers in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Src | is the pointer to the 16-word array of the HMAC key. |

This function is used to write HMAC key to the digest registers for key preprocessing. The size of pui32Src must be 512 bytes. If the key is less than 512 bytes, then it must be padded with zeros.

Definition at line 1014 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_MODE_CLOSE_HASH, SHAMD5_MODE_HMAC_KEY_PROC, SHAMD5_MODE_HMAC_OUTER_HASH, SHAMD5_O_MODE, and SHAMD5_O_ODIGEST_A.

| void SHAMD5HMACPPKeyGenerate | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Key, | ||

| uint32_t * | pui32PPKey | ||

| ) |

Process an HMAC key using the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Key | is a pointer to an array that contains the key to be processed. |

| pui32PPKey | is the pointer to the array that contains the pre-processed key. |

This function processes an HMAC key using the SHA/MD5. The resultant pre-processed key can then be used with later HMAC operations to speed processing time.

The pui32Key array must be 16 words (512 bits) long. If the key is less than 512 bits, it must be padded with zeros. The pui32PPKey array must each be 16 words (512 bits) long.

Definition at line 943 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_MODE_HMAC_KEY_PROC, SHAMD5_O_IRQSTATUS, SHAMD5_O_LENGTH, SHAMD5_O_MODE, and SHAMD5_O_ODIGEST_A.

| void SHAMD5HMACPPKeySet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Src | ||

| ) |

Writes a pre-processed HMAC key to the digest registers in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Src | is the pointer to the 16-word array of the HMAC key. |

This function is used to write HMAC key to the digest registers for key preprocessing. The size of pui32Src must be 512 bytes. If the key is less than 512 bytes, then it must be padded with zeros.

Definition at line 1058 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_MODE_CLOSE_HASH, SHAMD5_MODE_HMAC_OUTER_HASH, SHAMD5_O_DIGEST_COUNT, SHAMD5_O_MODE, and SHAMD5_O_ODIGEST_A.

| void SHAMD5HMACProcess | ( | uint32_t | ui32Base, |

| uint32_t * | pui32DataSrc, | ||

| uint32_t | ui32DataLength, | ||

| uint32_t * | pui32HashResult | ||

| ) |

Compute a HMAC with key pre-processing using the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32DataSrc | is a pointer to an array of data that contains the data that is to be hashed. |

| ui32DataLength | specifies the length of the data to be hashed in bytes. |

| pui32HashResult | is a pointer to an array that holds the result of the hashing operation. |

This function computes a HMAC with the given data using the SHA/MD5 module with a preprocessed key.

The length of the hash result is dependent on the algorithm that is selected with the ui32Algo argument. The following table shows the correct array size for each algorithm:

| MD5 | 4 Words (128 bits) | | SHA-1 | 5 Words (160 bits) | | SHA-224 | 7 Words (224 bits) |

Definition at line 881 of file shamd5.c.

References _SHAMD5DataWriteMultiple(), ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_O_IRQSTATUS, SHAMD5HashLengthSet(), and SHAMD5ResultRead().

| void SHAMD5IntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears interrupt sources in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| ui32IntFlags | contains desired interrupts to disable. |

ui32IntFlags must be a logical OR of one or more of the following values:

Definition at line 318 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_INPUT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_INT_PARTHASH_READY, and SHAMD5_O_DMAIC.

| void SHAMD5IntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disable interrupt sources in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| ui32IntFlags | contains desired interrupts to disable. |

ui32IntFlags must be a logical OR of one or more of the following values:

Definition at line 270 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_INPUT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_INT_PARTHASH_READY, SHAMD5_O_DMAIM, SHAMD5_O_IRQENABLE, SHAMD5_O_SYSCONFIG, and SHAMD5_SYSCONFIG_IT_EN.

| void SHAMD5IntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enable interrupt sources in the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| ui32IntFlags | contains desired interrupts to enable. |

This function enables interrupt sources in the SHA/MD5 module. ui32IntFlags must be a logical OR of one or more of the following values:

Definition at line 225 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_INT_CONTEXT_READY, SHAMD5_INT_INPUT_READY, SHAMD5_INT_OUTPUT_READY, SHAMD5_INT_PARTHASH_READY, SHAMD5_O_DMAIM, SHAMD5_O_IRQENABLE, SHAMD5_O_SYSCONFIG, and SHAMD5_SYSCONFIG_IT_EN.

| void SHAMD5IntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| pfnHandler | is a pointer to the function to be called when the enabled SHA/MD5 interrupts occur. |

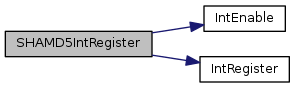

This function registers the interrupt handler in the interrupt vector table, and enables SHA/MD5 interrupts on the interrupt controller; specific SHA/MD5 interrupt sources must be enabled using SHAMD5IntEnable(). The interrupt handler being registered must clear the source of the interrupt using SHAMD5IntClear().

If the application is using a static interrupt vector table stored in flash, then it is not necessary to register the interrupt handler this way. Instead, IntEnable() should be used to enable SHA/MD5 interrupts on the interrupt controller.

Definition at line 363 of file shamd5.c.

References ASSERT, INT_SHA0_TM4C129, IntEnable(), IntRegister(), and SHAMD5_BASE.

| uint32_t SHAMD5IntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Get the interrupt status of the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

| bMasked | is false if the raw interrupt status is required and true if the masked interrupt status is required. |

This function returns the current value of the IRQSTATUS register. The value will be a logical OR of the following:

Definition at line 172 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_O_DMAMIS, SHAMD5_O_DMARIS, SHAMD5_O_IRQENABLE, and SHAMD5_O_IRQSTATUS.

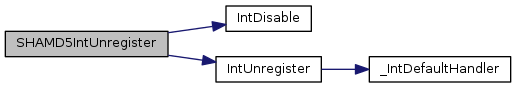

| void SHAMD5IntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters an interrupt handler for the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

This function unregisters the previously registered interrupt handler and disables the interrupt in the interrupt controller.

Definition at line 397 of file shamd5.c.

References ASSERT, INT_SHA0_TM4C129, IntDisable(), IntUnregister(), and SHAMD5_BASE.

| void SHAMD5Reset | ( | uint32_t | ui32Base | ) |

Resets the SHA/MD5 module.

| ui32Base | is the base address of the SHA/MD5 module. |

This function performs a soft-reset of the SHA/MD5 module using the SYSCONFIG register.

Definition at line 71 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_O_SYSCONFIG, SHAMD5_O_SYSSTATUS, SHAMD5_SYSCONFIG_SIDLE_FORCE, SHAMD5_SYSCONFIG_SIDLE_M, SHAMD5_SYSCONFIG_SOFTRESET, and SHAMD5_SYSSTATUS_RESETDONE.

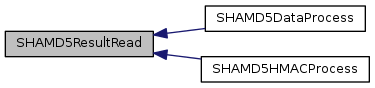

| void SHAMD5ResultRead | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Dest | ||

| ) |

Reads the result of a hashing operation.

| ui32Base | is the base address of the SHA/MD5 module. |

| pui32Dest | is the pointer to the 16-word array of data that will be written. |

This function does not return until the module is ready to accept data and the data has been written.

Definition at line 592 of file shamd5.c.

References ASSERT, HWREG, SHAMD5_BASE, SHAMD5_MODE_ALGO_M, SHAMD5_MODE_ALGO_MD5, SHAMD5_MODE_ALGO_SHA1, SHAMD5_MODE_ALGO_SHA224, SHAMD5_MODE_ALGO_SHA256, SHAMD5_O_IDIGEST_A, and SHAMD5_O_MODE.

Referenced by SHAMD5DataProcess(), and SHAMD5HMACProcess().