|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Functions | |

| bool | WatchdogRunning (uint32_t ui32Base) |

| void | WatchdogEnable (uint32_t ui32Base) |

| void | WatchdogResetEnable (uint32_t ui32Base) |

| void | WatchdogResetDisable (uint32_t ui32Base) |

| void | WatchdogLock (uint32_t ui32Base) |

| void | WatchdogUnlock (uint32_t ui32Base) |

| bool | WatchdogLockState (uint32_t ui32Base) |

| void | WatchdogReloadSet (uint32_t ui32Base, uint32_t ui32LoadVal) |

| uint32_t | WatchdogReloadGet (uint32_t ui32Base) |

| uint32_t | WatchdogValueGet (uint32_t ui32Base) |

| void | WatchdogIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | WatchdogIntUnregister (uint32_t ui32Base) |

| void | WatchdogIntEnable (uint32_t ui32Base) |

| uint32_t | WatchdogIntStatus (uint32_t ui32Base, bool bMasked) |

| void | WatchdogIntClear (uint32_t ui32Base) |

| void | WatchdogIntTypeSet (uint32_t ui32Base, uint32_t ui32Type) |

| void | WatchdogStallEnable (uint32_t ui32Base) |

| void | WatchdogStallDisable (uint32_t ui32Base) |

| void WatchdogEnable | ( | uint32_t | ui32Base | ) |

Enables the watchdog timer.

| ui32Base | is the base address of the watchdog timer module. |

This function enables the watchdog timer counter and interrupt.

Definition at line 97 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_CTL_INTEN, and WDT_O_CTL.

| void WatchdogIntClear | ( | uint32_t | ui32Base | ) |

Clears the watchdog timer interrupt.

| ui32Base | is the base address of the watchdog timer module. |

The watchdog timer interrupt source is cleared, so that it no longer asserts.

Definition at line 501 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_O_ICR, and WDT_RIS_WDTRIS.

| void WatchdogIntEnable | ( | uint32_t | ui32Base | ) |

Enables the watchdog timer interrupt.

| ui32Base | is the base address of the watchdog timer module. |

This function enables the watchdog timer interrupt.

Definition at line 427 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_CTL_INTEN, and WDT_O_CTL.

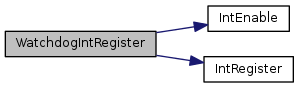

| void WatchdogIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the watchdog timer interrupt.

| ui32Base | is the base address of the watchdog timer module. |

| pfnHandler | is a pointer to the function to be called when the watchdog timer interrupt occurs. |

This function does the actual registering of the interrupt handler. This function also enables the global interrupt in the interrupt controller; the watchdog timer interrupt must be enabled via WatchdogEnable(). It is the interrupt handler's responsibility to clear the interrupt source via WatchdogIntClear().

Definition at line 353 of file watchdog.c.

References ASSERT, INT_WATCHDOG_TM4C123, IntEnable(), IntRegister(), WATCHDOG0_BASE, and WATCHDOG1_BASE.

| uint32_t WatchdogIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current watchdog timer interrupt status.

| ui32Base | is the base address of the watchdog timer module. |

| bMasked | is false if the raw interrupt status is required and true if the masked interrupt status is required. |

This function returns the interrupt status for the watchdog timer module. Either the raw interrupt status or the status of interrupt that is allowed to reflect to the processor can be returned.

Definition at line 457 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_O_MIS, and WDT_O_RIS.

| void WatchdogIntTypeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Type | ||

| ) |

Sets the type of interrupt generated by the watchdog.

| ui32Base | is the base address of the watchdog timer module. |

| ui32Type | is the type of interrupt to generate. |

This function sets the type of interrupt that is generated if the watchdog timer expires. ui32Type can be either WATCHDOG_INT_TYPE_INT to generate a standard interrupt (the default) or WATCHDOG_INT_TYPE_NMI to generate a non-maskable interrupt (NMI).

When configured to generate an NMI, the watchdog interrupt must still be enabled with WatchdogIntEnable(), and it must still be cleared inside the NMI handler with WatchdogIntClear().

Definition at line 539 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WATCHDOG_INT_TYPE_INT, WATCHDOG_INT_TYPE_NMI, WDT_CTL_INTTYPE, and WDT_O_CTL.

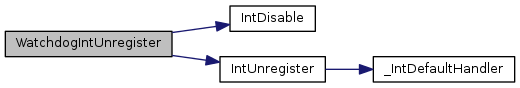

| void WatchdogIntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters an interrupt handler for the watchdog timer interrupt.

| ui32Base | is the base address of the watchdog timer module. |

This function does the actual unregistering of the interrupt handler. This function clears the handler to be called when a watchdog timer interrupt occurs. This function also masks off the interrupt in the interrupt controller so that the interrupt handler no longer is called.

Definition at line 395 of file watchdog.c.

References ASSERT, INT_WATCHDOG_TM4C123, IntDisable(), IntUnregister(), WATCHDOG0_BASE, and WATCHDOG1_BASE.

| void WatchdogLock | ( | uint32_t | ui32Base | ) |

Enables the watchdog timer lock mechanism.

| ui32Base | is the base address of the watchdog timer module. |

This function locks out write access to the watchdog timer registers.

Definition at line 178 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_LOCK_LOCKED, and WDT_O_LOCK.

| bool WatchdogLockState | ( | uint32_t | ui32Base | ) |

Gets the state of the watchdog timer lock mechanism.

| ui32Base | is the base address of the watchdog timer module. |

This function returns the lock state of the watchdog timer registers.

Definition at line 230 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_LOCK_LOCKED, and WDT_O_LOCK.

| uint32_t WatchdogReloadGet | ( | uint32_t | ui32Base | ) |

Gets the watchdog timer reload value.

| ui32Base | is the base address of the watchdog timer module. |

This function gets the value that is loaded into the watchdog timer when the count reaches zero for the first time.

Definition at line 288 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, and WDT_O_LOAD.

| void WatchdogReloadSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32LoadVal | ||

| ) |

Sets the watchdog timer reload value.

| ui32Base | is the base address of the watchdog timer module. |

| ui32LoadVal | is the load value for the watchdog timer. |

This function configures the value to load into the watchdog timer when the count reaches zero for the first time; if the watchdog timer is running when this function is called, then the value is immediately loaded into the watchdog timer counter. If the ui32LoadVal parameter is 0, then an interrupt is immediately generated.

Definition at line 262 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, and WDT_O_LOAD.

| void WatchdogResetDisable | ( | uint32_t | ui32Base | ) |

Disables the watchdog timer reset.

| ui32Base | is the base address of the watchdog timer module. |

This function disables the capability of the watchdog timer to issue a reset to the processor after a second timeout condition.

Definition at line 153 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_CTL_RESEN, and WDT_O_CTL.

| void WatchdogResetEnable | ( | uint32_t | ui32Base | ) |

Enables the watchdog timer reset.

| ui32Base | is the base address of the watchdog timer module. |

This function enables the capability of the watchdog timer to issue a reset to the processor after a second timeout condition.

Definition at line 125 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_CTL_RESEN, and WDT_O_CTL.

| bool WatchdogRunning | ( | uint32_t | ui32Base | ) |

Determines if the watchdog timer is enabled.

| ui32Base | is the base address of the watchdog timer module. |

This function checks to see if the watchdog timer is enabled.

Definition at line 70 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_CTL_INTEN, and WDT_O_CTL.

| void WatchdogStallDisable | ( | uint32_t | ui32Base | ) |

Disables stalling of the watchdog timer during debug events.

| ui32Base | is the base address of the watchdog timer module. |

This function disables the debug mode stall of the watchdog timer. By doing so, the watchdog timer continues to count regardless of the processor debug state.

Definition at line 604 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_O_TEST, and WDT_TEST_STALL.

| void WatchdogStallEnable | ( | uint32_t | ui32Base | ) |

Enables stalling of the watchdog timer during debug events.

| ui32Base | is the base address of the watchdog timer module. |

This function allows the watchdog timer to stop counting when the processor is stopped by the debugger. By doing so, the watchdog is prevented from expiring (typically almost immediately from a human time perspective) and resetting the system (if reset is enabled). The watchdog instead expires after the appropriate number of processor cycles have been executed while debugging (or at the appropriate time after the processor has been restarted).

Definition at line 575 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_O_TEST, and WDT_TEST_STALL.

| void WatchdogUnlock | ( | uint32_t | ui32Base | ) |

Disables the watchdog timer lock mechanism.

| ui32Base | is the base address of the watchdog timer module. |

This function enables write access to the watchdog timer registers.

Definition at line 204 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, WDT_LOCK_UNLOCK, and WDT_O_LOCK.

| uint32_t WatchdogValueGet | ( | uint32_t | ui32Base | ) |

Gets the current watchdog timer value.

| ui32Base | is the base address of the watchdog timer module. |

This function reads the current value of the watchdog timer.

Definition at line 313 of file watchdog.c.

References ASSERT, HWREG, WATCHDOG0_BASE, WATCHDOG1_BASE, and WDT_O_VALUE.