|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Macros | |

| #define | PWM_GEN_BADDR(_mod_, _gen_) ((_mod_) + (_gen_)) |

| #define | PWM_GEN_EXT_BADDR(_mod_, _gen_) |

| #define | PWM_OUT_BADDR(_mod_, _out_) ((_mod_) + ((_out_) & 0xFFFFFFC0)) |

| #define | PWM_IS_OUTPUT_ODD(_out_) ((_out_) & 0x00000001) |

Functions | |

| void | PWMGenConfigure (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Config) |

| void | PWMGenPeriodSet (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Period) |

| uint32_t | PWMGenPeriodGet (uint32_t ui32Base, uint32_t ui32Gen) |

| void | PWMGenEnable (uint32_t ui32Base, uint32_t ui32Gen) |

| void | PWMGenDisable (uint32_t ui32Base, uint32_t ui32Gen) |

| void | PWMPulseWidthSet (uint32_t ui32Base, uint32_t ui32PWMOut, uint32_t ui32Width) |

| uint32_t | PWMPulseWidthGet (uint32_t ui32Base, uint32_t ui32PWMOut) |

| void | PWMDeadBandEnable (uint32_t ui32Base, uint32_t ui32Gen, uint16_t ui16Rise, uint16_t ui16Fall) |

| void | PWMDeadBandDisable (uint32_t ui32Base, uint32_t ui32Gen) |

| void | PWMSyncUpdate (uint32_t ui32Base, uint32_t ui32GenBits) |

| void | PWMSyncTimeBase (uint32_t ui32Base, uint32_t ui32GenBits) |

| void | PWMOutputState (uint32_t ui32Base, uint32_t ui32PWMOutBits, bool bEnable) |

| void | PWMOutputInvert (uint32_t ui32Base, uint32_t ui32PWMOutBits, bool bInvert) |

| void | PWMOutputFaultLevel (uint32_t ui32Base, uint32_t ui32PWMOutBits, bool bDriveHigh) |

| void | PWMOutputFault (uint32_t ui32Base, uint32_t ui32PWMOutBits, bool bFaultSuppress) |

| static uint32_t | _PWMGenIntNumberGet (uint32_t ui32Base, uint32_t ui32Gen) |

| void | PWMGenIntRegister (uint32_t ui32Base, uint32_t ui32Gen, void(*pfnIntHandler)(void)) |

| void | PWMGenIntUnregister (uint32_t ui32Base, uint32_t ui32Gen) |

| static uint32_t | _PWMFaultIntNumberGet (uint32_t ui32Base) |

| void | PWMFaultIntRegister (uint32_t ui32Base, void(*pfnIntHandler)(void)) |

| void | PWMFaultIntUnregister (uint32_t ui32Base) |

| void | PWMGenIntTrigEnable (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32IntTrig) |

| void | PWMGenIntTrigDisable (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32IntTrig) |

| uint32_t | PWMGenIntStatus (uint32_t ui32Base, uint32_t ui32Gen, bool bMasked) |

| void | PWMGenIntClear (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Ints) |

| void | PWMIntEnable (uint32_t ui32Base, uint32_t ui32GenFault) |

| void | PWMIntDisable (uint32_t ui32Base, uint32_t ui32GenFault) |

| void | PWMFaultIntClear (uint32_t ui32Base) |

| uint32_t | PWMIntStatus (uint32_t ui32Base, bool bMasked) |

| void | PWMFaultIntClearExt (uint32_t ui32Base, uint32_t ui32FaultInts) |

| void | PWMGenFaultConfigure (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32MinFaultPeriod, uint32_t ui32FaultSenses) |

| void | PWMGenFaultTriggerSet (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Group, uint32_t ui32FaultTriggers) |

| uint32_t | PWMGenFaultTriggerGet (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Group) |

| uint32_t | PWMGenFaultStatus (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Group) |

| void | PWMGenFaultClear (uint32_t ui32Base, uint32_t ui32Gen, uint32_t ui32Group, uint32_t ui32FaultTriggers) |

| void | PWMClockSet (uint32_t ui32Base, uint32_t ui32Config) |

| uint32_t | PWMClockGet (uint32_t ui32Base) |

| void | PWMOutputUpdateMode (uint32_t ui32Base, uint32_t ui32PWMOutBits, uint32_t ui32Mode) |

| #define PWM_GEN_BADDR | ( | _mod_, | |

| _gen_ | |||

| ) | ((_mod_) + (_gen_)) |

Definition at line 64 of file pwm.c.

Referenced by PWMDeadBandDisable(), PWMDeadBandEnable(), PWMGenConfigure(), PWMGenDisable(), PWMGenEnable(), PWMGenFaultConfigure(), PWMGenFaultTriggerGet(), PWMGenFaultTriggerSet(), PWMGenIntClear(), PWMGenIntStatus(), PWMGenIntTrigDisable(), PWMGenIntTrigEnable(), PWMGenPeriodGet(), and PWMGenPeriodSet().

| #define PWM_GEN_EXT_BADDR | ( | _mod_, | |

| _gen_ | |||

| ) |

Definition at line 66 of file pwm.c.

Referenced by PWMGenFaultClear(), PWMGenFaultConfigure(), and PWMGenFaultStatus().

| #define PWM_IS_OUTPUT_ODD | ( | _out_ | ) | ((_out_) & 0x00000001) |

Definition at line 71 of file pwm.c.

Referenced by PWMPulseWidthGet(), and PWMPulseWidthSet().

| #define PWM_OUT_BADDR | ( | _mod_, | |

| _out_ | |||

| ) | ((_mod_) + ((_out_) & 0xFFFFFFC0)) |

Definition at line 69 of file pwm.c.

Referenced by PWMPulseWidthGet(), and PWMPulseWidthSet().

|

static |

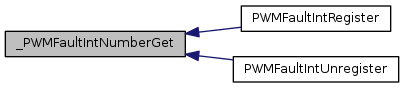

Gets the PWM fault interrupt number.

| ui32Base | is the base address of the PWM module. |

This function returns the fault interrupt number of the corresponding PWM module.

Definition at line 1179 of file pwm.c.

References CLASS_IS_TM4C123, CLASS_IS_TM4C129, INT_PWM0_FAULT_TM4C123, INT_PWM0_FAULT_TM4C129, INT_PWM1_FAULT_TM4C123, and PWM0_BASE.

Referenced by PWMFaultIntRegister(), and PWMFaultIntUnregister().

|

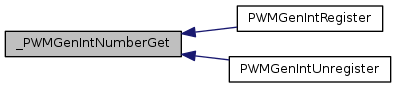

static |

Gets the PWM generator interrupt number.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator in question. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function returns the interrupt number of the corresponding PWM generator.

Definition at line 923 of file pwm.c.

References CLASS_IS_TM4C123, CLASS_IS_TM4C129, INT_PWM0_0_TM4C123, INT_PWM0_0_TM4C129, INT_PWM0_1_TM4C129, INT_PWM0_2_TM4C129, INT_PWM0_3_TM4C129, INT_PWM1_0_TM4C123, INT_PWM1_1_TM4C123, INT_PWM1_2_TM4C123, INT_PWM1_3_TM4C123, PWM0_BASE, PWM1_BASE, PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, and PWM_GEN_3.

Referenced by PWMGenIntRegister(), and PWMGenIntUnregister().

| uint32_t PWMClockGet | ( | uint32_t | ui32Base | ) |

Gets the current PWM clock configuration.

| ui32Base | is the base address of the PWM module. |

This function returns the current PWM clock configuration.

Definition at line 2030 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_CC_PWMDIV_M, PWM_CC_USEPWM, PWM_O_CC, and PWM_SYSCLK_DIV_1.

| void PWMClockSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Sets the PWM clock configuration.

| ui32Base | is the base address of the PWM module. |

| ui32Config | is the configuration for the PWM clock; it must be one of PWM_SYSCLK_DIV_1, PWM_SYSCLK_DIV_2, PWM_SYSCLK_DIV_4, PWM_SYSCLK_DIV_8, PWM_SYSCLK_DIV_16, PWM_SYSCLK_DIV_32, or PWM_SYSCLK_DIV_64. |

This function sets the PWM clock divider as the PWM clock source. It also configures the clock frequency to the PWM module as a division of the system clock. This clock is used by the PWM module to generate PWM signals; its rate forms the basis for all PWM signals.

Definition at line 1990 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_CC_PWMDIV_M, PWM_CC_USEPWM, PWM_O_CC, PWM_SYSCLK_DIV_16, PWM_SYSCLK_DIV_2, PWM_SYSCLK_DIV_32, PWM_SYSCLK_DIV_4, PWM_SYSCLK_DIV_64, and PWM_SYSCLK_DIV_8.

| void PWMDeadBandDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen | ||

| ) |

Disables the PWM dead band output.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to modify. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function disables the dead band mode for the specified PWM generator. Doing so decouples the OutA and OutB signals.

Definition at line 624 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_DBCTL, and PWM_X_DBCTL_ENABLE.

| void PWMDeadBandEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint16_t | ui16Rise, | ||

| uint16_t | ui16Fall | ||

| ) |

Enables the PWM dead band output and sets the dead band delays.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to modify. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui16Rise | specifies the width of delay from the rising edge. |

| ui16Fall | specifies the width of delay from the falling edge. |

This function sets the dead bands for the specified PWM generator, where the dead bands are defined as the number of PWM clock ticks from the rising or falling edge of the generator's OutA signal. Note that this function causes the coupling of OutB to OutA.

Definition at line 581 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_DBCTL, PWM_O_X_DBFALL, PWM_O_X_DBRISE, and PWM_X_DBCTL_ENABLE.

| void PWMFaultIntClear | ( | uint32_t | ui32Base | ) |

Clears the fault interrupt for a PWM module.

| ui32Base | is the base address of the PWM module. |

This function clears the fault interrupt by writing to the appropriate bit of the interrupt status register for the selected PWM module.

This function clears only the FAULT0 interrupt and is retained for backwards compatibility. It is recommended that PWMFaultIntClearExt() be used instead because it supports all fault interrupts supported on devices with and without extended PWM fault handling support.

Definition at line 1564 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_ISC_INTFAULT0, and PWM_O_ISC.

| void PWMFaultIntClearExt | ( | uint32_t | ui32Base, |

| uint32_t | ui32FaultInts | ||

| ) |

Clears the fault interrupt for a PWM module.

| ui32Base | is the base address of the PWM module. |

| ui32FaultInts | specifies the fault interrupts to clear. |

This function clears one or more fault interrupts by writing to the appropriate bit of the PWM interrupt status register. The parameter ui32FaultInts must be the logical OR of any of PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, or PWM_INT_FAULT3.

The fault interrupts are derived by performing a logical OR of each of the configured fault trigger signals for a given generator. Therefore, these interrupts are not directly related to the four possible FAULTn inputs to the device but indicate that a fault has been signaled to one of the four possible PWM generators.

Definition at line 1646 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, PWM_INT_FAULT3, and PWM_O_ISC.

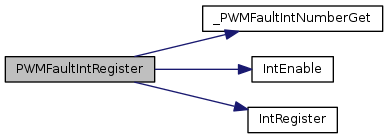

| void PWMFaultIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnIntHandler | ||

| ) |

Registers an interrupt handler for a fault condition detected in a PWM module.

| ui32Base | is the base address of the PWM module. |

| pfnIntHandler | is a pointer to the function to be called when the PWM fault interrupt occurs. |

This function ensures that the interrupt handler specified by pfnIntHandler is called when a fault interrupt is detected for the selected PWM module. This function also enables the PWM fault interrupt in the NVIC; the PWM fault interrupt must also be enabled at the module level using PWMIntEnable().

Definition at line 1221 of file pwm.c.

References _PWMFaultIntNumberGet(), ASSERT, IntEnable(), IntRegister(), PWM0_BASE, and PWM1_BASE.

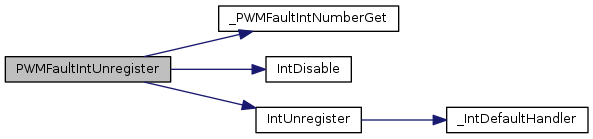

| void PWMFaultIntUnregister | ( | uint32_t | ui32Base | ) |

Removes the PWM fault condition interrupt handler.

| ui32Base | is the base address of the PWM module. |

This function removes the interrupt handler for a PWM fault interrupt from the selected PWM module. This function also disables the PWM fault interrupt in the NVIC; the PWM fault interrupt must also be disabled at the module level using PWMIntDisable().

Definition at line 1266 of file pwm.c.

References _PWMFaultIntNumberGet(), ASSERT, IntDisable(), IntUnregister(), PWM0_BASE, and PWM1_BASE.

| void PWMGenConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Config | ||

| ) |

Configures a PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to configure. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Config | is the configuration for the PWM generator. |

This function is used to set the mode of operation for a PWM generator. The counting mode, synchronization mode, and debug behavior are all configured. After configuration, the generator is left in the disabled state.

A PWM generator can count in two different modes: count down mode or count up/down mode. In count down mode, it counts from a value down to zero, and then resets to the preset value, producing left-aligned PWM signals (that is, the rising edge of the two PWM signals produced by the generator occur at the same time). In count up/down mode, it counts up from zero to the preset value, counts back down to zero, and then repeats the process, producing center-aligned PWM signals (that is, the middle of the high/low period of the PWM signals produced by the generator occurs at the same time).

When the PWM generator parameters (period and pulse width) are modified, their effect on the output PWM signals can be delayed. In synchronous mode, the parameter updates are not applied until a synchronization event occurs. This mode allows multiple parameters to be modified and take effect simultaneously, instead of one at a time. Additionally, parameters to multiple PWM generators in synchronous mode can be updated simultaneously, allowing them to be treated as if they were a unified generator. In non-synchronous mode, the parameter updates are not delayed until a synchronization event. In either mode, the parameter updates only occur when the counter is at zero to help prevent oddly formed PWM signals during the update (that is, a PWM pulse that is too short or too long).

The PWM generator can either pause or continue running when the processor is stopped via the debugger. If configured to pause, it continues to count until it reaches zero, at which point it pauses until the processor is restarted. If configured to continue running, it keeps counting as if nothing had happened.

The ui32Config parameter contains the desired configuration. It is the logical OR of the following:

Setting PWM_GEN_MODE_FAULT_MINPER allows an application to set the minimum duration of a PWM fault signal. Faults are signaled for at least this time even if the external fault pin deasserts earlier. Care should be taken when using this mode because during the fault signal period, the fault interrupt from the PWM generator remains asserted. The fault interrupt handler may, therefore, reenter immediately if it exits prior to expiration of the fault timer.

Definition at line 200 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_CTL, PWM_O_X_GENA, PWM_O_X_GENB, PWM_X_CTL_CMPAUPD, PWM_X_CTL_CMPBUPD, PWM_X_CTL_DBCTLUPD_M, PWM_X_CTL_DBFALLUPD_M, PWM_X_CTL_DBRISEUPD_M, PWM_X_CTL_DEBUG, PWM_X_CTL_FLTSRC, PWM_X_CTL_GENAUPD_M, PWM_X_CTL_GENBUPD_M, PWM_X_CTL_LATCH, PWM_X_CTL_LOADUPD, PWM_X_CTL_MINFLTPER, PWM_X_CTL_MODE, PWM_X_GENA_ACTCMPAD_ZERO, PWM_X_GENA_ACTCMPAU_ONE, PWM_X_GENA_ACTLOAD_ONE, PWM_X_GENB_ACTCMPBD_ZERO, PWM_X_GENB_ACTCMPBU_ONE, and PWM_X_GENB_ACTLOAD_ONE.

| void PWMGenDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen | ||

| ) |

Disables the timer/counter for a PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to be disabled. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function blocks the PWM clock from driving the timer/counter for the specified generator block.

Definition at line 412 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_CTL, and PWM_X_CTL_ENABLE.

| void PWMGenEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen | ||

| ) |

Enables the timer/counter for a PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to be enabled. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function allows the PWM clock to drive the timer/counter for the specified generator block.

Definition at line 383 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_CTL, and PWM_X_CTL_ENABLE.

| void PWMGenFaultClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Group, | ||

| uint32_t | ui32FaultTriggers | ||

| ) |

Clears one or more latched fault triggers for a given PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator for which fault trigger states are being queried. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Group | indicates the subset of faults that are being queried. This parameter must be PWM_FAULT_GROUP_0 or PWM_FAULT_GROUP_1. |

| ui32FaultTriggers | is the set of fault triggers which are to be cleared. |

This function allows an application to clear the fault triggers for a given PWM generator. This function is only required if PWMGenConfigure() has previously been called with flag PWM_GEN_MODE_FAULT_LATCHED in parameter ui32Config.

Definition at line 1930 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_FAULT_DCMP0, PWM_FAULT_DCMP1, PWM_FAULT_DCMP2, PWM_FAULT_DCMP3, PWM_FAULT_DCMP4, PWM_FAULT_DCMP5, PWM_FAULT_DCMP6, PWM_FAULT_DCMP7, PWM_FAULT_FAULT0, PWM_FAULT_FAULT1, PWM_FAULT_FAULT2, PWM_FAULT_FAULT3, PWM_FAULT_GROUP_0, PWM_FAULT_GROUP_1, PWM_GEN_EXT_BADDR, PWM_O_X_FLTSTAT0, and PWM_O_X_FLTSTAT1.

| void PWMGenFaultConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32MinFaultPeriod, | ||

| uint32_t | ui32FaultSenses | ||

| ) |

Configures the minimum fault period and fault pin senses for a given PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator for which fault configuration is being set. This function must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32MinFaultPeriod | is the minimum fault active period expressed in PWM clock cycles. |

| ui32FaultSenses | indicates which sense of each FAULT input should be considered the ``asserted'' state. Valid values are logical OR combinations of PWM_FAULTn_SENSE_HIGH and PWM_FAULTn_SENSE_LOW. |

This function configures the minimum fault period for a given generator along with the sense of each of the 4 possible fault inputs. The minimum fault period is expressed in PWM clock cycles and takes effect only if PWMGenConfigure() is called with flag PWM_GEN_MODE_FAULT_PER set in the ui32Config parameter. When a fault input is asserted, the minimum fault period timer ensures that it remains asserted for at least the number of clock cycles specified.

Definition at line 1691 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_FAULT0_SENSE_HIGH, PWM_FAULT0_SENSE_LOW, PWM_FAULT1_SENSE_HIGH, PWM_FAULT1_SENSE_LOW, PWM_FAULT2_SENSE_HIGH, PWM_FAULT2_SENSE_LOW, PWM_FAULT3_SENSE_HIGH, PWM_FAULT3_SENSE_LOW, PWM_GEN_BADDR, PWM_GEN_EXT_BADDR, PWM_O_X_FLTSEN, PWM_O_X_MINFLTPER, and PWM_X_MINFLTPER_M.

| uint32_t PWMGenFaultStatus | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Group | ||

| ) |

Returns the current state of the fault triggers for a given PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator for which fault trigger states are being queried. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Group | indicates the subset of faults that are being queried. This parameter must be PWM_FAULT_GROUP_0 or PWM_FAULT_GROUP_1. |

This function allows an application to query the current state of each of the fault trigger inputs to a given PWM generator. The current state of each fault trigger input is returned unless PWMGenConfigure() has previously been called with flag PWM_GEN_MODE_FAULT_LATCHED in the ui32Config parameter, in which case the returned status is the latched fault trigger status.

If latched faults are configured, the application must call PWMGenFaultClear() to clear each trigger.

Definition at line 1881 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_FAULT_GROUP_0, PWM_FAULT_GROUP_1, PWM_GEN_EXT_BADDR, PWM_O_X_FLTSTAT0, and PWM_O_X_FLTSTAT1.

| uint32_t PWMGenFaultTriggerGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Group | ||

| ) |

Returns the set of fault triggers currently configured for a given PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator for which fault triggers are being queried. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Group | indicates the subset of faults that are being queried. This parameter must be PWM_FAULT_GROUP_0 or PWM_FAULT_GROUP_1. |

This function allows an application to query the current set of inputs that contribute to the generation of a fault condition to a given PWM generator.

Definition at line 1822 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_FAULT_GROUP_0, PWM_FAULT_GROUP_1, PWM_GEN_BADDR, PWM_O_X_FLTSRC0, and PWM_O_X_FLTSRC1.

| void PWMGenFaultTriggerSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Group, | ||

| uint32_t | ui32FaultTriggers | ||

| ) |

Configures the set of fault triggers for a given PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator for which fault triggers are being set. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Group | indicates the subset of possible faults that are to be configured. This parameter must be PWM_FAULT_GROUP_0 or PWM_FAULT_GROUP_1. |

| ui32FaultTriggers | defines the set of inputs that are to contribute towards generation of the fault signal to the given PWM generator. For PWM_FAULT_GROUP_0, this is the logical OR of PWM_FAULT_FAULT0, PWM_FAULT_FAULT1, PWM_FAULT_FAULT2, or PWM_FAULT_FAULT3. For PWM_FAULT_GROUP_1, this is the logical OR of PWM_FAULT_DCMP0, PWM_FAULT_DCMP1, PWM_FAULT_DCMP2, PWM_FAULT_DCMP3, PWM_FAULT_DCMP4, PWM_FAULT_DCMP5, PWM_FAULT_DCMP6, or PWM_FAULT_DCMP7. |

This function allows selection of the set of fault inputs that is combined to generate a fault condition to a given PWM generator. By default, all generators use only FAULT0 (for backwards compatibility) but if PWMGenConfigure() is called with flag PWM_GEN_MODE_FAULT_SRC in the ui32Config parameter, extended fault handling is enabled and this function must be called to configure the fault triggers.

The fault signal to the PWM generator is generated by ORing together each of the signals specified in the ui32FaultTriggers parameter after having adjusted the sense of each FAULTn input based on the configuration previously set using a call to PWMGenFaultConfigure().

Definition at line 1759 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_FAULT_DCMP0, PWM_FAULT_DCMP1, PWM_FAULT_DCMP2, PWM_FAULT_DCMP3, PWM_FAULT_DCMP4, PWM_FAULT_DCMP5, PWM_FAULT_DCMP6, PWM_FAULT_DCMP7, PWM_FAULT_FAULT0, PWM_FAULT_FAULT1, PWM_FAULT_FAULT2, PWM_FAULT_FAULT3, PWM_FAULT_GROUP_0, PWM_FAULT_GROUP_1, PWM_GEN_BADDR, PWM_O_X_FLTSRC0, and PWM_O_X_FLTSRC1.

| void PWMGenIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Ints | ||

| ) |

Clears the specified interrupt(s) for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to query. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Ints | specifies the interrupts to be cleared. |

This function clears the specified interrupt(s) by writing a 1 to the specified bits of the interrupt status register for the specified PWM generator. The ui32Ints parameter is the logical OR of PWM_INT_CNT_ZERO, PWM_INT_CNT_LOAD, PWM_INT_CNT_AU, PWM_INT_CNT_AD, PWM_INT_CNT_BU, or PWM_INT_CNT_BD.

Definition at line 1451 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_INT_CNT_AD, PWM_INT_CNT_AU, PWM_INT_CNT_BD, PWM_INT_CNT_BU, PWM_INT_CNT_LOAD, PWM_INT_CNT_ZERO, and PWM_O_X_ISC.

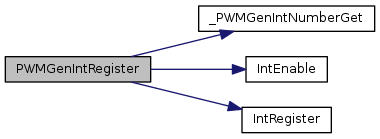

| void PWMGenIntRegister | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| void(*)(void) | pfnIntHandler | ||

| ) |

Registers an interrupt handler for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator in question. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| pfnIntHandler | is a pointer to the function to be called when the PWM generator interrupt occurs. |

This function ensures that the interrupt handler specified by pfnIntHandler is called when an interrupt is detected for the specified PWM generator block. This function also enables the corresponding PWM generator interrupt in the interrupt controller; individual generator interrupts and interrupt sources must be enabled with PWMIntEnable() and PWMGenIntTrigEnable().

Definition at line 1088 of file pwm.c.

References _PWMGenIntNumberGet(), ASSERT, IntEnable(), IntRegister(), PWM0_BASE, and PWM1_BASE.

| uint32_t PWMGenIntStatus | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| bool | bMasked | ||

| ) |

Gets interrupt status for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to query. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| bMasked | specifies whether masked or raw interrupt status is returned. |

If bMasked is set as true, then the masked interrupt status is returned; otherwise, the raw interrupt status is returned.

Definition at line 1396 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_ISC, and PWM_O_X_RIS.

| void PWMGenIntTrigDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32IntTrig | ||

| ) |

Disables interrupts for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to have interrupts and triggers disabled. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32IntTrig | specifies the interrupts and triggers to be disabled. |

This function masks the specified interrupt(s) and trigger(s) by clearing the specified bits of the interrupt/trigger enable register for the specified PWM generator. The ui32IntTrig parameter is the logical OR of PWM_INT_CNT_ZERO, PWM_INT_CNT_LOAD, PWM_INT_CNT_AU, PWM_INT_CNT_AD, PWM_INT_CNT_BU, PWM_INT_CNT_BD, PWM_TR_CNT_ZERO, PWM_TR_CNT_LOAD, PWM_TR_CNT_AU, PWM_TR_CNT_AD, PWM_TR_CNT_BU, or PWM_TR_CNT_BD.

Definition at line 1357 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_INT_CNT_AD, PWM_INT_CNT_AU, PWM_INT_CNT_BD, PWM_INT_CNT_BU, PWM_INT_CNT_LOAD, PWM_INT_CNT_ZERO, PWM_O_X_INTEN, PWM_TR_CNT_AD, PWM_TR_CNT_AU, PWM_TR_CNT_BD, PWM_TR_CNT_BU, PWM_TR_CNT_LOAD, and PWM_TR_CNT_ZERO.

| void PWMGenIntTrigEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32IntTrig | ||

| ) |

Enables interrupts and triggers for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to have interrupts and triggers enabled. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32IntTrig | specifies the interrupts and triggers to be enabled. |

This function unmasks the specified interrupt(s) and trigger(s) by setting the specified bits of the interrupt/trigger enable register for the specified PWM generator. The ui32IntTrig parameter is the logical OR of PWM_INT_CNT_ZERO, PWM_INT_CNT_LOAD, PWM_INT_CNT_AU, PWM_INT_CNT_AD, PWM_INT_CNT_BU, PWM_INT_CNT_BD, PWM_TR_CNT_ZERO, PWM_TR_CNT_LOAD, PWM_TR_CNT_AU, PWM_TR_CNT_AD, PWM_TR_CNT_BU, or PWM_TR_CNT_BD.

Definition at line 1315 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_INT_CNT_AD, PWM_INT_CNT_AU, PWM_INT_CNT_BD, PWM_INT_CNT_BU, PWM_INT_CNT_LOAD, PWM_INT_CNT_ZERO, PWM_O_X_INTEN, PWM_TR_CNT_AD, PWM_TR_CNT_AU, PWM_TR_CNT_BD, PWM_TR_CNT_BU, PWM_TR_CNT_LOAD, and PWM_TR_CNT_ZERO.

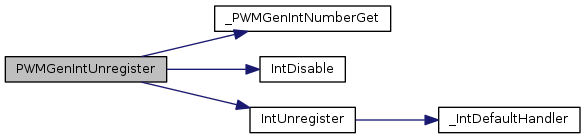

| void PWMGenIntUnregister | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen | ||

| ) |

Removes an interrupt handler for the specified PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator in question. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function unregisters the interrupt handler for the specified PWM generator block. This function also disables the corresponding PWM generator interrupt in the interrupt controller; individual generator interrupts and interrupt sources must be disabled with PWMIntDisable() and PWMGenIntTrigDisable().

Definition at line 1138 of file pwm.c.

References _PWMGenIntNumberGet(), ASSERT, IntDisable(), IntUnregister(), PWM0_BASE, and PWM1_BASE.

| uint32_t PWMGenPeriodGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen | ||

| ) |

Gets the period of a PWM generator block.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to query. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

This function gets the period of the specified PWM generator block. The period of the generator block is defined as the number of PWM clock ticks between pulses on the generator block zero signal.

If the update of the counter for the specified PWM generator has yet to be completed, the value returned may not be the active period. The value returned is the programmed period, measured in PWM clock ticks.

Definition at line 336 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_CTL, PWM_O_X_LOAD, and PWM_X_CTL_MODE.

| void PWMGenPeriodSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Gen, | ||

| uint32_t | ui32Period | ||

| ) |

Sets the period of a PWM generator.

| ui32Base | is the base address of the PWM module. |

| ui32Gen | is the PWM generator to be modified. This parameter must be one of PWM_GEN_0, PWM_GEN_1, PWM_GEN_2, or PWM_GEN_3. |

| ui32Period | specifies the period of PWM generator output, measured in clock ticks. |

This function sets the period of the specified PWM generator block, where the period of the generator block is defined as the number of PWM clock ticks between pulses on the generator block zero signal.

Definition at line 278 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_BADDR, PWM_O_X_CTL, PWM_O_X_LOAD, and PWM_X_CTL_MODE.

| void PWMIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32GenFault | ||

| ) |

Disables generator and fault interrupts for a PWM module.

| ui32Base | is the base address of the PWM module. |

| ui32GenFault | contains the interrupts to be disabled. This parameter must be a logical OR of any of PWM_INT_GEN_0, PWM_INT_GEN_1, PWM_INT_GEN_2, PWM_INT_GEN_3, PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, or PWM_INT_FAULT3. |

This function masks the specified interrupt(s) by clearing the specified bits of the interrupt enable register for the selected PWM module.

Definition at line 1520 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, PWM_INT_FAULT3, PWM_INT_GEN_0, PWM_INT_GEN_1, PWM_INT_GEN_2, PWM_INT_GEN_3, and PWM_O_INTEN.

| void PWMIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32GenFault | ||

| ) |

Enables generator and fault interrupts for a PWM module.

| ui32Base | is the base address of the PWM module. |

| ui32GenFault | contains the interrupts to be enabled. This parameter must be a logical OR of any of PWM_INT_GEN_0, PWM_INT_GEN_1, PWM_INT_GEN_2, PWM_INT_GEN_3, PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, or PWM_INT_FAULT3. |

This function unmasks the specified interrupt(s) by setting the specified bits of the interrupt enable register for the selected PWM module.

Definition at line 1486 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_INT_FAULT0, PWM_INT_FAULT1, PWM_INT_FAULT2, PWM_INT_FAULT3, PWM_INT_GEN_0, PWM_INT_GEN_1, PWM_INT_GEN_2, PWM_INT_GEN_3, and PWM_O_INTEN.

| uint32_t PWMIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the interrupt status for a PWM module.

| ui32Base | is the base address of the PWM module. |

| bMasked | specifies whether masked or raw interrupt status is returned. |

If bMasked is set as true, then the masked interrupt status is returned; otherwise, the raw interrupt status is returned.

Definition at line 1595 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_ISC, and PWM_O_RIS.

| void PWMOutputFault | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOutBits, | ||

| bool | bFaultSuppress | ||

| ) |

Specifies the state of PWM outputs in response to a fault condition.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOutBits | are the PWM outputs to be modified. This parameter must be the logical OR of any of PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, or PWM_OUT_7_BIT. |

| bFaultSuppress | determines if the signal is suppressed or passed through during an active fault condition. |

This function sets the fault handling characteristics of the selected PWM outputs. The outputs are selected using the parameter ui32PWMOutBits. The parameter bFaultSuppress determines the fault handling characteristics for the selected outputs. If bFaultSuppress is true, then the selected outputs are made inactive. If bFaultSuppress is false, then the selected outputs are unaffected by the detected fault.

On devices supporting extended PWM fault handling, the state the affected output pins are driven to can be configured with PWMOutputFaultLevel(). If not configured, or if the device does not support extended PWM fault handling, affected outputs are driven low on a fault condition.

Definition at line 883 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_FAULT, PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, and PWM_OUT_7_BIT.

| void PWMOutputFaultLevel | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOutBits, | ||

| bool | bDriveHigh | ||

| ) |

Specifies the level of PWM outputs suppressed in response to a fault condition.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOutBits | are the PWM outputs to be modified. This parameter must be the logical OR of any of PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, or PWM_OUT_7_BIT. |

| bDriveHigh | determines if the signal is driven high or low during an active fault condition. |

This function determines whether a PWM output pin that is suppressed in response to a fault condition is driven high or low. The affected outputs are selected using the parameter ui32PWMOutBits. The parameter bDriveHigh determines the output level for the pins identified by ui32PWMOutBits. If bDriveHigh is true then the selected outputs are driven high when a fault is detected. If it is false, the pins are driven low.

In a fault condition, pins which have not been configured to be suppressed via a call to PWMOutputFault() are unaffected by this function.

Definition at line 830 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_FAULTVAL, PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, and PWM_OUT_7_BIT.

| void PWMOutputInvert | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOutBits, | ||

| bool | bInvert | ||

| ) |

Selects the inversion mode for PWM outputs.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOutBits | are the PWM outputs to be modified. This parameter must be the logical OR of any of PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, or PWM_OUT_7_BIT. |

| bInvert | determines if the signal is inverted or passed through. |

This function is used to select the inversion mode for the selected PWM outputs. The outputs are selected using the parameter ui32PWMOutBits. The parameter bInvert determines the inversion mode for the selected outputs. If bInvert is true, this function causes the specified PWM output signals to be inverted or made active low. If bInvert is false, the specified outputs are passed through as is or made active high.

Definition at line 774 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_INVERT, PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, and PWM_OUT_7_BIT.

| void PWMOutputState | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOutBits, | ||

| bool | bEnable | ||

| ) |

Enables or disables PWM outputs.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOutBits | are the PWM outputs to be modified. This parameter must be the logical OR of any of PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, or PWM_OUT_7_BIT. |

| bEnable | determines if the signal is enabled or disabled. |

This function enables or disables the selected PWM outputs. The outputs are selected using the parameter ui32PWMOutBits. The parameter bEnable determines the state of the selected outputs. If bEnable is true, then the selected PWM outputs are enabled, or placed in the active state. If bEnable is false, then the selected outputs are disabled or placed in the inactive state.

Definition at line 726 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_ENABLE, PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, and PWM_OUT_7_BIT.

| void PWMOutputUpdateMode | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOutBits, | ||

| uint32_t | ui32Mode | ||

| ) |

Sets the update mode or synchronization mode to the PWM outputs.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOutBits | are the PWM outputs to be modified. This parameter must be the logical OR of any of PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, or PWM_OUT_7_BIT. |

| ui32Mode | specifies the enable update mode to use when enabling or disabling PWM outputs. |

This function sets one of three possible update modes to enable or disable the requested PWM outputs. The ui32Mode parameter controls when changes made via calls to PWMOutputState() take effect. Possible values are:

Definition at line 2088 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_O_ENUPD, PWM_OUT_0_BIT, PWM_OUT_1_BIT, PWM_OUT_2_BIT, PWM_OUT_3_BIT, PWM_OUT_4_BIT, PWM_OUT_5_BIT, PWM_OUT_6_BIT, PWM_OUT_7_BIT, PWM_OUTPUT_MODE_NO_SYNC, PWM_OUTPUT_MODE_SYNC_GLOBAL, and PWM_OUTPUT_MODE_SYNC_LOCAL.

| uint32_t PWMPulseWidthGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOut | ||

| ) |

Gets the pulse width of a PWM output.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOut | is the PWM output to query. This parameter must be one of PWM_OUT_0, PWM_OUT_1, PWM_OUT_2, PWM_OUT_3, PWM_OUT_4, PWM_OUT_5, PWM_OUT_6, or PWM_OUT_7. |

This function gets the currently programmed pulse width for the specified PWM output. If the update of the comparator for the specified output has yet to be completed, the value returned may not be the active pulse width. The value returned is the programmed pulse width, measured in PWM clock ticks.

Definition at line 518 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_IS_OUTPUT_ODD, PWM_O_X_CMPA, PWM_O_X_CMPB, PWM_O_X_CTL, PWM_O_X_LOAD, PWM_OUT_BADDR, and PWM_X_CTL_MODE.

| void PWMPulseWidthSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32PWMOut, | ||

| uint32_t | ui32Width | ||

| ) |

Sets the pulse width for the specified PWM output.

| ui32Base | is the base address of the PWM module. |

| ui32PWMOut | is the PWM output to modify. This parameter must be one of PWM_OUT_0, PWM_OUT_1, PWM_OUT_2, PWM_OUT_3, PWM_OUT_4, PWM_OUT_5, PWM_OUT_6, or PWM_OUT_7. |

| ui32Width | specifies the width of the positive portion of the pulse. |

This function sets the pulse width for the specified PWM output, where the pulse width is defined as the number of PWM clock ticks.

Definition at line 447 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_IS_OUTPUT_ODD, PWM_O_X_CMPA, PWM_O_X_CMPB, PWM_O_X_CTL, PWM_O_X_LOAD, PWM_OUT_BADDR, and PWM_X_CTL_MODE.

| void PWMSyncTimeBase | ( | uint32_t | ui32Base, |

| uint32_t | ui32GenBits | ||

| ) |

Synchronizes the counters in one or multiple PWM generator blocks.

| ui32Base | is the base address of the PWM module. |

| ui32GenBits | are the PWM generator blocks to be synchronized. This parameter must be the logical OR of any of PWM_GEN_0_BIT, PWM_GEN_1_BIT, PWM_GEN_2_BIT, or PWM_GEN_3_BIT. |

For the selected PWM module, this function synchronizes the time base of the generator blocks by causing the specified generator counters to be reset to zero.

Definition at line 688 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_0_BIT, PWM_GEN_1_BIT, PWM_GEN_2_BIT, PWM_GEN_3_BIT, and PWM_O_SYNC.

| void PWMSyncUpdate | ( | uint32_t | ui32Base, |

| uint32_t | ui32GenBits | ||

| ) |

Synchronizes all pending updates.

| ui32Base | is the base address of the PWM module. |

| ui32GenBits | are the PWM generator blocks to be updated. This parameter must be the logical OR of any of PWM_GEN_0_BIT, PWM_GEN_1_BIT, PWM_GEN_2_BIT, or PWM_GEN_3_BIT. |

For the selected PWM generators, this function causes all queued updates to the period or pulse width to be applied the next time the corresponding counter becomes zero.

Definition at line 656 of file pwm.c.

References ASSERT, HWREG, PWM0_BASE, PWM1_BASE, PWM_GEN_0_BIT, PWM_GEN_1_BIT, PWM_GEN_2_BIT, PWM_GEN_3_BIT, and PWM_O_CTL.