|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Macros | |

| #define | ADC_SEQ (ADC_O_SSMUX0) |

| #define | ADC_SEQ_STEP (ADC_O_SSMUX1 - ADC_O_SSMUX0) |

| #define | ADC_SSMUX (ADC_O_SSMUX0 - ADC_O_SSMUX0) |

| #define | ADC_SSEMUX (ADC_O_SSEMUX0 - ADC_O_SSMUX0) |

| #define | ADC_SSCTL (ADC_O_SSCTL0 - ADC_O_SSMUX0) |

| #define | ADC_SSFIFO (ADC_O_SSFIFO0 - ADC_O_SSMUX0) |

| #define | ADC_SSFSTAT (ADC_O_SSFSTAT0 - ADC_O_SSMUX0) |

| #define | ADC_SSOP (ADC_O_SSOP0 - ADC_O_SSMUX0) |

| #define | ADC_SSDC (ADC_O_SSDC0 - ADC_O_SSMUX0) |

| #define | ADC_SSTSH (ADC_O_SSTSH0 - ADC_O_SSMUX0) |

Functions | |

| static uint_fast8_t | _ADCIntNumberGet (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCIntRegister (uint32_t ui32Base, uint32_t ui32SequenceNum, void(*pfnHandler)(void)) |

| void | ADCIntUnregister (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCIntDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCIntEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| uint32_t | ADCIntStatus (uint32_t ui32Base, uint32_t ui32SequenceNum, bool bMasked) |

| void | ADCIntClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Trigger, uint32_t ui32Priority) |

| void | ADCSequenceStepConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Step, uint32_t ui32Config) |

| int32_t | ADCSequenceOverflow (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceOverflowClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| int32_t | ADCSequenceUnderflow (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceUnderflowClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| int32_t | ADCSequenceDataGet (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t *pui32Buffer) |

| void | ADCProcessorTrigger (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSoftwareOversampleConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Factor) |

| void | ADCSoftwareOversampleStepConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Step, uint32_t ui32Config) |

| void | ADCSoftwareOversampleDataGet (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t *pui32Buffer, uint32_t ui32Count) |

| void | ADCHardwareOversampleConfigure (uint32_t ui32Base, uint32_t ui32Factor) |

| void | ADCComparatorConfigure (uint32_t ui32Base, uint32_t ui32Comp, uint32_t ui32Config) |

| void | ADCComparatorRegionSet (uint32_t ui32Base, uint32_t ui32Comp, uint32_t ui32LowRef, uint32_t ui32HighRef) |

| void | ADCComparatorReset (uint32_t ui32Base, uint32_t ui32Comp, bool bTrigger, bool bInterrupt) |

| void | ADCComparatorIntDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCComparatorIntEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| uint32_t | ADCComparatorIntStatus (uint32_t ui32Base) |

| void | ADCComparatorIntClear (uint32_t ui32Base, uint32_t ui32Status) |

| void | ADCIntDisableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | ADCIntEnableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| uint32_t | ADCIntStatusEx (uint32_t ui32Base, bool bMasked) |

| void | ADCIntClearEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | ADCReferenceSet (uint32_t ui32Base, uint32_t ui32Ref) |

| uint32_t | ADCReferenceGet (uint32_t ui32Base) |

| void | ADCPhaseDelaySet (uint32_t ui32Base, uint32_t ui32Phase) |

| uint32_t | ADCPhaseDelayGet (uint32_t ui32Base) |

| void | ADCSequenceDMAEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceDMADisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| bool | ADCBusy (uint32_t ui32Base) |

| void | ADCClockConfigSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32ClockDiv) |

| uint32_t | ADCClockConfigGet (uint32_t ui32Base, uint32_t *pui32ClockDiv) |

Variables | |

| static uint8_t | g_pui8OversampleFactor [3] |

| #define ADC_SEQ (ADC_O_SSMUX0) |

Definition at line 64 of file adc.c.

Referenced by ADCSequenceDataGet(), ADCSequenceStepConfigure(), ADCSoftwareOversampleDataGet(), and ADCSoftwareOversampleStepConfigure().

| #define ADC_SEQ_STEP (ADC_O_SSMUX1 - ADC_O_SSMUX0) |

Definition at line 65 of file adc.c.

Referenced by ADCSequenceDataGet(), ADCSequenceStepConfigure(), ADCSoftwareOversampleDataGet(), and ADCSoftwareOversampleStepConfigure().

| #define ADC_SSCTL (ADC_O_SSCTL0 - ADC_O_SSMUX0) |

Definition at line 68 of file adc.c.

Referenced by ADCSequenceStepConfigure(), and ADCSoftwareOversampleStepConfigure().

| #define ADC_SSDC (ADC_O_SSDC0 - ADC_O_SSMUX0) |

Definition at line 72 of file adc.c.

Referenced by ADCSequenceStepConfigure().

| #define ADC_SSEMUX (ADC_O_SSEMUX0 - ADC_O_SSMUX0) |

Definition at line 67 of file adc.c.

Referenced by ADCSequenceStepConfigure(), and ADCSoftwareOversampleStepConfigure().

| #define ADC_SSFIFO (ADC_O_SSFIFO0 - ADC_O_SSMUX0) |

Definition at line 69 of file adc.c.

Referenced by ADCSequenceDataGet(), and ADCSoftwareOversampleDataGet().

| #define ADC_SSFSTAT (ADC_O_SSFSTAT0 - ADC_O_SSMUX0) |

Definition at line 70 of file adc.c.

Referenced by ADCSequenceDataGet().

| #define ADC_SSMUX (ADC_O_SSMUX0 - ADC_O_SSMUX0) |

Definition at line 66 of file adc.c.

Referenced by ADCSequenceStepConfigure(), and ADCSoftwareOversampleStepConfigure().

| #define ADC_SSOP (ADC_O_SSOP0 - ADC_O_SSMUX0) |

Definition at line 71 of file adc.c.

Referenced by ADCSequenceStepConfigure().

| #define ADC_SSTSH (ADC_O_SSTSH0 - ADC_O_SSMUX0) |

Definition at line 73 of file adc.c.

Referenced by ADCSequenceStepConfigure().

|

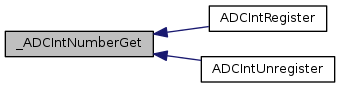

static |

Returns the interrupt number for a given ADC base address and sequence number.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function returns the interrupt number for the ADC module and sequence number provided in the ui32Base and ui32SequenceNum parameters.

Definition at line 99 of file adc.c.

References ADC0_BASE, CLASS_IS_TM4C123, CLASS_IS_TM4C129, INT_ADC0SS0_TM4C123, INT_ADC0SS0_TM4C129, and INT_ADC1SS0_TM4C129.

Referenced by ADCIntRegister(), and ADCIntUnregister().

| bool ADCBusy | ( | uint32_t | ui32Base | ) |

Determines whether the ADC is busy or not.

| ui32Base | is the base address of the ADC. |

This function allows the caller to determine whether or not the ADC is currently sampling . If false is returned, then the ADC is not sampling data.

Use this function to detect that the ADC is finished sampling data before putting the device into deep sleep. Before using this function, it is highly recommended that the event trigger is changed to ADC_TRIGGER_NEVER on all enabled sequencers to prevent the ADC from starting after checking the busy status.

Definition at line 1834 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_ACTSS_BUSY, ADC_O_ACTSS, ASSERT, and HWREG.

| uint32_t ADCClockConfigGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32ClockDiv | ||

| ) |

Returns the clock configuration for the ADC.

| ui32Base | is the base address of the ADC to configure, which must always be ADC0_BASE. |

| pui32ClockDiv | is a pointer to the input clock divider for the clock selected by the ADC_CLOCK_SRC in use by the ADCs. |

This function returns the ADC clock configuration and the clock divider for the ADCs.

Example: Read the current ADC clock configuration.

//! uint32_t ui32Config, ui32ClockDiv; //! //! // //! // Read the current ADC clock configuration. //! // //! ui32Config = ADCClockConfigGet(ADC0_BASE, &ui32ClockDiv); //!

\return The current clock configuration of the ADC defined as a combination of one of \b ADC_CLOCK_SRC_PLL, \b ADC_CLOCK_SRC_PIOSC, \b ADC_CLOCK_SRC_MOSC, or \b ADC_CLOCK_SRC_ALTCLK logical ORed with one of \b ADC_CLOCK_RATE_FULL, \b ADC_CLOCK_RATE_HALF, \b ADC_CLOCK_RATE_QUARTER, or \b ADC_CLOCK_RATE_EIGHTH. See ADCClockConfigSet() for more information on these values.

Definition at line 1978 of file adc.c.

References ADC0_BASE, ADC_CC_CLKDIV_M, ADC_CC_CLKDIV_S, ADC_O_CC, ADC_O_PC, ADC_PC_SR_M, ASSERT, and HWREG.

| void ADCClockConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32ClockDiv | ||

| ) |

Sets the clock configuration for the ADC.

| ui32Base | is the base address of the ADC to configure, which must always be ADC0_BASE. |

| ui32Config | is a combination of the ADC_CLOCK_SRC_ and ADC_CLOCK_RATE_* values used to configure the ADC clock input. |

| ui32ClockDiv | is the input clock divider for the clock selected by the ADC_CLOCK_SRC value. |

This function is used to configure the input clock to the ADC modules. The clock configuration is shared across ADC units so ui32Base must always be ADC0_BASE. The ui32Config value is logical OR of one of the ADC_CLOCK_RATE_ and one of the ADC_CLOCK_SRC_ values defined below. The ADC_CLOCK_SRC_* values determine the input clock for the ADC. Not all values are available on all devices so check the device data sheet to determine value configuration options. Regardless of the source, the final frequency for TM4C123x devices must be 16 MHz and for TM4C129x parts after dividing must be between 16 and 32 MHz.

ADC_CLOCK_RATE values control how often samples are provided back to the application. The values are the following:

The ui32ClockDiv parameter allows for dividing a higher frequency down into the valid range for the ADCs. This parameter is typically only used ADC_CLOCK_SRC_PLL option because it is the only clock value that can be with the in the correct range to use the divider. The actual value ranges from 1 to 64.

Example: ADC Clock Configurations

//! //! // //! // Configure the ADC to use PIOSC divided by one (16 MHz) and sample at //! // half the rate. //! // //! ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PIOSC | ADC_CLOCK_RATE_HALF, 1); //! //! ... //! //! // //! // Configure the ADC to use PLL at 480 MHz divided by 24 to get an ADC //! // clock of 20 MHz. //! // //! ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADC_CLOCK_RATE_FULL, 24); //!

\return None.

Definition at line 1916 of file adc.c.

References ADC0_BASE, ADC_CC_CLKDIV_M, ADC_CC_CLKDIV_S, ADC_CC_CS_M, ADC_CLOCK_RATE_FULL, ADC_O_CC, ADC_O_PC, ADC_PC_SR_M, ASSERT, and HWREG.

| void ADCComparatorConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32Comp, | ||

| uint32_t | ui32Config | ||

| ) |

Configures an ADC digital comparator.

| ui32Base | is the base address of the ADC module. |

| ui32Comp | is the index of the comparator to configure. |

| ui32Config | is the configuration of the comparator. |

This function configures a comparator. The ui32Config parameter is the result of a logical OR operation between the ADC_COMP_TRIG_xxx, and ADC_COMP_INT_xxx values.

The ADC_COMP_TRIG_xxx term can take on the following values:

The ADC_COMP_INT_xxx term can take on the following values:

Definition at line 1222 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_DCCTL0, ASSERT, and HWREG.

| void ADCComparatorIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32Status | ||

| ) |

Clears sample sequence comparator interrupt source.

| ui32Base | is the base address of the ADC module. |

| ui32Status | is the bit-mapped interrupts status to clear. |

The specified interrupt status is cleared.

Definition at line 1414 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_DCISC, ASSERT, and HWREG.

| void ADCComparatorIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Disables a sample sequence comparator interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function disables the requested sample sequence comparator interrupt.

Definition at line 1334 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ASSERT, and HWREG.

| void ADCComparatorIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Enables a sample sequence comparator interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function enables the requested sample sequence comparator interrupt.

Definition at line 1361 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ASSERT, and HWREG.

| uint32_t ADCComparatorIntStatus | ( | uint32_t | ui32Base | ) |

Gets the current comparator interrupt status.

| ui32Base | is the base address of the ADC module. |

This function returns the digital comparator interrupt status bits. This status is sequence agnostic.

Definition at line 1388 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_DCISC, ASSERT, and HWREG.

| void ADCComparatorRegionSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Comp, | ||

| uint32_t | ui32LowRef, | ||

| uint32_t | ui32HighRef | ||

| ) |

Defines the ADC digital comparator regions.

| ui32Base | is the base address of the ADC module. |

| ui32Comp | is the index of the comparator to configure. |

| ui32LowRef | is the reference point for the low/mid band threshold. |

| ui32HighRef | is the reference point for the mid/high band threshold. |

The ADC digital comparator operation is based on three ADC value regions:

Definition at line 1258 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_DCCMP0, ASSERT, and HWREG.

| void ADCComparatorReset | ( | uint32_t | ui32Base, |

| uint32_t | ui32Comp, | ||

| bool | bTrigger, | ||

| bool | bInterrupt | ||

| ) |

Resets the current ADC digital comparator conditions.

| ui32Base | is the base address of the ADC module. |

| ui32Comp | is the index of the comparator. |

| bTrigger | is the flag to indicate reset of Trigger conditions. |

| bInterrupt | is the flag to indicate reset of Interrupt conditions. |

Because the digital comparator uses current and previous ADC values, this function allows the comparator to be reset to its initial value to prevent stale data from being used when a sequence is enabled.

Definition at line 1293 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_DCRIC, ASSERT, and HWREG.

| void ADCHardwareOversampleConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32Factor | ||

| ) |

Configures the hardware oversampling factor of the ADC.

| ui32Base | is the base address of the ADC module. |

| ui32Factor | is the number of samples to be averaged. |

This function configures the hardware oversampling for the ADC, which can be used to provide better resolution on the sampled data. Oversampling is accomplished by averaging multiple samples from the same analog input. Six different oversampling rates are supported; 2x, 4x, 8x, 16x, 32x, and 64x. Specifying an oversampling factor of zero disables hardware oversampling.

Hardware oversampling applies uniformly to all sample sequencers. It does not reduce the depth of the sample sequencers like the software oversampling APIs; each sample written into the sample sequencer FIFO is a fully oversampled analog input reading.

Enabling hardware averaging increases the precision of the ADC at the cost of throughput. For example, enabling 4x oversampling reduces the throughput of a 250 k samples/second ADC to 62.5 k samples/second.

Definition at line 1124 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_SAC, ASSERT, and HWREG.

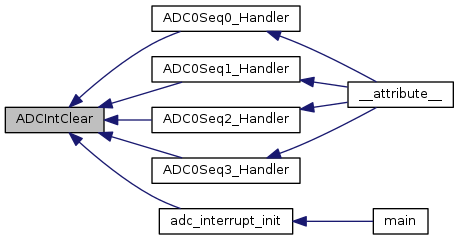

| void ADCIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Clears sample sequence interrupt source.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

The specified sample sequence interrupt is cleared, so that it no longer asserts. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

Definition at line 363 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ISC, ASSERT, and HWREG.

Referenced by ADC0Seq0_Handler(), ADC0Seq1_Handler(), ADC0Seq2_Handler(), ADC0Seq3_Handler(), and adc_interrupt_init().

| void ADCIntClearEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears the specified ADC interrupt sources.

| ui32Base | is the base address of the ADC port. |

| ui32IntFlags | is the bit mask of the interrupt sources to disable. |

Clears the interrupt for the specified interrupt source(s).

The ui32IntFlags parameter is the logical OR of the ADC_INT_* values. See the ADCIntEnableEx() function for the list of possible ADC_INT* values.

Definition at line 1606 of file adc.c.

References ADC_O_ISC, and HWREG.

| void ADCIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Disables a sample sequence interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function disables the requested sample sequence interrupt.

Definition at line 234 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ASSERT, and HWREG.

| void ADCIntDisableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables ADC interrupt sources.

| ui32Base | is the base address of the ADC module. |

| ui32IntFlags | is the bit mask of the interrupt sources to disable. |

This function disables the indicated ADC interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1461 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ASSERT, and HWREG.

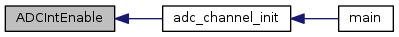

| void ADCIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Enables a sample sequence interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function enables the requested sample sequence interrupt. Any outstanding interrupts are cleared before enabling the sample sequence interrupt.

Definition at line 263 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ADC_O_ISC, ASSERT, and HWREG.

Referenced by adc_channel_init().

| void ADCIntEnableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables ADC interrupt sources.

| ui32Base | is the base address of the ADC module. |

| ui32IntFlags | is the bit mask of the interrupt sources to disable. |

This function enables the indicated ADC interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1508 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_IM, ASSERT, and HWREG.

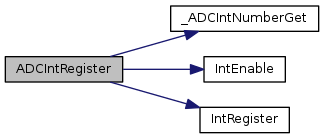

| void ADCIntRegister | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for an ADC interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| pfnHandler | is a pointer to the function to be called when the ADC sample sequence interrupt occurs. |

This function sets the handler to be called when a sample sequence interrupt occurs. This function enables the global interrupt in the interrupt controller; the sequence interrupt must be enabled with ADCIntEnable(). It is the interrupt handler's responsibility to clear the interrupt source via ADCIntClear().

Definition at line 148 of file adc.c.

References _ADCIntNumberGet(), ADC0_BASE, ADC1_BASE, ASSERT, IntEnable(), and IntRegister().

| uint32_t ADCIntStatus | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| bool | bMasked | ||

| ) |

Gets the current interrupt status.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| bMasked | is false if the raw interrupt status is required and true if the masked interrupt status is required. |

This function returns the interrupt status for the specified sample sequence. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 299 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ISC, ADC_O_RIS, ASSERT, and HWREG.

| uint32_t ADCIntStatusEx | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets interrupt status for the specified ADC module.

| ui32Base | is the base address of the ADC module. |

| bMasked | specifies whether masked or raw interrupt status is returned. |

If bMasked is set as true, then the masked interrupt status is returned; otherwise, the raw interrupt status is returned.

Definition at line 1538 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_INT_DCON_SS0, ADC_INT_DCON_SS1, ADC_INT_DCON_SS2, ADC_INT_DCON_SS3, ADC_O_ISC, ADC_O_RIS, ADC_RIS_INRDC, ASSERT, and HWREG.

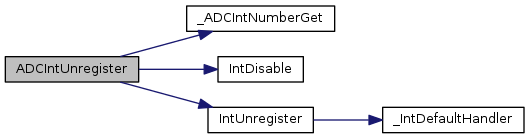

| void ADCIntUnregister | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Unregisters the interrupt handler for an ADC interrupt.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function unregisters the interrupt handler. This function disables the global interrupt in the interrupt controller; the sequence interrupt must be disabled via ADCIntDisable().

Definition at line 194 of file adc.c.

References _ADCIntNumberGet(), ADC0_BASE, ADC1_BASE, ASSERT, IntDisable(), and IntUnregister().

| uint32_t ADCPhaseDelayGet | ( | uint32_t | ui32Base | ) |

Gets the phase delay between a trigger and the start of a sequence.

| ui32Base | is the base address of the ADC module. |

This function gets the current phase delay between the detection of an ADC trigger event and the start of the sample sequence.

Definition at line 1745 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_SPC, ASSERT, and HWREG.

| void ADCPhaseDelaySet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Phase | ||

| ) |

Sets the phase delay between a trigger and the start of a sequence.

| ui32Base | is the base address of the ADC module. |

| ui32Phase | is the phase delay, specified as one of ADC_PHASE_0, ADC_PHASE_22_5, ADC_PHASE_45, ADC_PHASE_67_5, ADC_PHASE_90, ADC_PHASE_112_5, ADC_PHASE_135, ADC_PHASE_157_5, ADC_PHASE_180, ADC_PHASE_202_5, ADC_PHASE_225, ADC_PHASE_247_5, ADC_PHASE_270, ADC_PHASE_292_5, ADC_PHASE_315, or ADC_PHASE_337_5. |

This function sets the phase delay between the detection of an ADC trigger event and the start of the sample sequence. By selecting a different phase delay for a pair of ADC modules (such as ADC_PHASE_0 and ADC_PHASE_180) and having each ADC module sample the same analog input, it is possible to increase the sampling rate of the analog input (with samples N, N+2, N+4, and so on, coming from the first ADC and samples N+1, N+3, N+5, and so on, coming from the second ADC). The ADC module has a single phase delay that is applied to all sample sequences within that module.

Definition at line 1707 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_SPC, ADC_PHASE_0, ADC_PHASE_112_5, ADC_PHASE_135, ADC_PHASE_157_5, ADC_PHASE_180, ADC_PHASE_202_5, ADC_PHASE_225, ADC_PHASE_22_5, ADC_PHASE_247_5, ADC_PHASE_270, ADC_PHASE_292_5, ADC_PHASE_315, ADC_PHASE_337_5, ADC_PHASE_45, ADC_PHASE_67_5, ADC_PHASE_90, ASSERT, and HWREG.

| void ADCProcessorTrigger | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Causes a processor trigger for a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number, with ADC_TRIGGER_WAIT or ADC_TRIGGER_SIGNAL optionally ORed into it. |

This function triggers a processor-initiated sample sequence if the sample sequence trigger is configured to ADC_TRIGGER_PROCESSOR. If ADC_TRIGGER_WAIT is ORed into the sequence number, the processor-initiated trigger is delayed until a later processor-initiated trigger to a different ADC module that specifies ADC_TRIGGER_SIGNAL, allowing multiple ADCs to start from a processor-initiated trigger in a synchronous manner.

Definition at line 884 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_PSSI, ASSERT, and HWREG.

| uint32_t ADCReferenceGet | ( | uint32_t | ui32Base | ) |

Returns the current setting of the ADC reference.

| ui32Base | is the base address of the ADC module. |

Returns the value of the ADC reference setting. The returned value is one of ADC_REF_INT, ADC_REF_EXT_3V, or ADC_REF_EXT_1V.

Definition at line 1667 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_CTL_VREF_M, ADC_O_CTL, ASSERT, and HWREG.

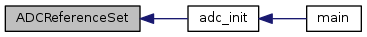

| void ADCReferenceSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Ref | ||

| ) |

Selects the ADC reference.

| ui32Base | is the base address of the ADC module. |

| ui32Ref | is the reference to use. |

The ADC reference is set as specified by ui32Ref. It must be one of ADC_REF_INT, ADC_REF_EXT_3V, or ADC_REF_EXT_1V for internal or external reference. If ADC_REF_INT is chosen, then an internal 3V reference is used and no external reference is needed. If ADC_REF_EXT_3V is chosen, then a 3V reference must be supplied to the AVREF pin. If ADC_REF_EXT_1V is chosen, then a 1V external reference must be supplied to the AVREF pin.

Definition at line 1634 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_CTL_VREF_M, ADC_O_CTL, ADC_REF_EXT_1V, ADC_REF_EXT_3V, ADC_REF_INT, ASSERT, and HWREG.

Referenced by adc_init().

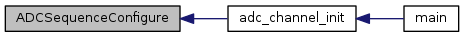

| void ADCSequenceConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t | ui32Trigger, | ||

| uint32_t | ui32Priority | ||

| ) |

Configures the trigger source and priority of a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| ui32Trigger | is the trigger source that initiates the sample sequence; must be one of the ADC_TRIGGER_* values. |

| ui32Priority | is the relative priority of the sample sequence with respect to the other sample sequences. |

This function configures the initiation criteria for a sample sequence. Valid sample sequencers range from zero to three; sequencer zero captures up to eight samples, sequencers one and two capture up to four samples, and sequencer three captures a single sample. The trigger condition and priority (with respect to other sample sequencer execution) are set.

The ui32Trigger parameter can take on the following values:

When ADC_TRIGGER_PWM0, ADC_TRIGGER_PWM1, ADC_TRIGGER_PWM2 or ADC_TRIGGER_PWM3 is specified, one of the following should be ORed into ui32Trigger to select the PWM module from which the triggers will be routed for this sequence:

Note that not all trigger sources are available on all Tiva family members; consult the data sheet for the device in question to determine the availability of triggers.

The ui32Priority parameter is a value between 0 and 3, where 0 represents the highest priority and 3 the lowest. Note that when programming the priority among a set of sample sequences, each must have unique priority; it is up to the caller to guarantee the uniqueness of the priorities.

Definition at line 502 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_EMUX, ADC_O_SSPRI, ADC_O_TSSEL, ADC_TRIGGER_ALWAYS, ADC_TRIGGER_COMP0, ADC_TRIGGER_COMP1, ADC_TRIGGER_COMP2, ADC_TRIGGER_EXTERNAL, ADC_TRIGGER_PROCESSOR, ADC_TRIGGER_PWM0, ADC_TRIGGER_PWM1, ADC_TRIGGER_PWM2, ADC_TRIGGER_PWM3, ADC_TRIGGER_PWM_MOD0, ADC_TRIGGER_PWM_MOD1, ADC_TRIGGER_TIMER, ASSERT, and HWREG.

Referenced by adc_channel_init().

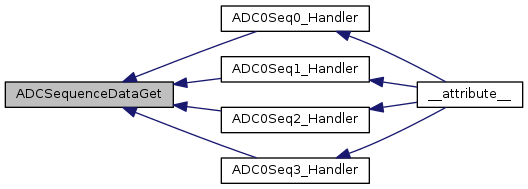

| int32_t ADCSequenceDataGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t * | pui32Buffer | ||

| ) |

Gets the captured data for a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| pui32Buffer | is the address where the data is stored. |

This function copies data from the specified sample sequencer output FIFO to a memory resident buffer. The number of samples available in the hardware FIFO are copied into the buffer, which is assumed to be large enough to hold that many samples. This function only returns the samples that are presently available, which may not be the entire sample sequence if it is in the process of being executed.

Definition at line 824 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_SEQ, ADC_SEQ_STEP, ADC_SSFIFO, ADC_SSFSTAT, ADC_SSFSTAT0_EMPTY, ASSERT, and HWREG.

Referenced by ADC0Seq0_Handler(), ADC0Seq1_Handler(), ADC0Seq2_Handler(), and ADC0Seq3_Handler().

| void ADCSequenceDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Disables a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

Prevents the specified sample sequence from being captured when its trigger is detected. A sample sequence must be disabled before it is configured.

Definition at line 419 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ACTSS, ASSERT, and HWREG.

Referenced by adc_channel_init().

| void ADCSequenceDMADisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Disables DMA for sample sequencers.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

Prevents the specified sample sequencer from generating DMA requests.

Definition at line 1799 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ACTSS, ASSERT, and HWREG.

| void ADCSequenceDMAEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Enables DMA for sample sequencers.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

Allows DMA requests to be generated based on the FIFO level of the sample sequencer.

Definition at line 1772 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ACTSS, ASSERT, and HWREG.

| void ADCSequenceEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Enables a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

Allows the specified sample sequence to be captured when its trigger is detected. A sample sequence must be configured before it is enabled.

Definition at line 391 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_ACTSS, ASSERT, and HWREG.

Referenced by adc_channel_init().

| int32_t ADCSequenceOverflow | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Determines if a sample sequence overflow occurred.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function determines if a sample sequence overflow has occurred. Overflow happens if the captured samples are not read from the FIFO before the next trigger occurs.

Definition at line 704 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_OSTAT, ASSERT, and HWREG.

| void ADCSequenceOverflowClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Clears the overflow condition on a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function clears an overflow condition on one of the sample sequences. The overflow condition must be cleared in order to detect a subsequent overflow condition (it otherwise causes no harm).

Definition at line 733 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_OSTAT, ASSERT, and HWREG.

| void ADCSequenceStepConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t | ui32Step, | ||

| uint32_t | ui32Config | ||

| ) |

Configure a step of the sample sequencer.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| ui32Step | is the step to be configured. |

| ui32Config | is the configuration of this step; must be a logical OR of ADC_CTL_TS, ADC_CTL_IE, ADC_CTL_END, ADC_CTL_D, one of the input channel selects (ADC_CTL_CH0 through ADC_CTL_CH23), and one of the digital comparator selects (ADC_CTL_CMP0 through ADC_CTL_CMP7). |

This function configures the ADC for one step of a sample sequence. The ADC can be configured for single-ended or differential operation (the ADC_CTL_D bit selects differential operation when set), the channel to be sampled can be chosen (the ADC_CTL_CH0 through ADC_CTL_CH23 values), and the internal temperature sensor can be selected (the ADC_CTL_TS bit). Additionally, this step can be defined as the last in the sequence (the ADC_CTL_END bit) and it can be configured to cause an interrupt when the step is complete (the ADC_CTL_IE bit). If the digital comparators are present on the device, this step may also be configured to send the ADC sample to the selected comparator using ADC_CTL_CMP0 through ADC_CTL_CMP7. The configuration is used by the ADC at the appropriate time when the trigger for this sequence occurs.

The ui32Step parameter determines the order in which the samples are captured by the ADC when the trigger occurs. It can range from zero to seven for the first sample sequencer, from zero to three for the second and third sample sequencer, and can only be zero for the fourth sample sequencer.

Differential mode only works with adjacent channel pairs (for example, 0 and 1). The channel select must be the number of the channel pair to sample (for example, ADC_CTL_CH0 for 0 and 1, or ADC_CTL_CH1 for 2 and 3) or undefined results are returned by the ADC. Additionally, if differential mode is selected when the temperature sensor is being sampled, undefined results are returned by the ADC.

It is the responsibility of the caller to ensure that a valid configuration is specified; this function does not check the validity of the specified configuration.

Definition at line 605 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_SEQ, ADC_SEQ_STEP, ADC_SSCTL, ADC_SSDC, ADC_SSEMUX, ADC_SSMUX, ADC_SSOP, ADC_SSTSH, ASSERT, and HWREG.

Referenced by adc_channel_init().

| int32_t ADCSequenceUnderflow | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Determines if a sample sequence underflow occurred.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function determines if a sample sequence underflow has occurred. Underflow happens if too many samples are read from the FIFO.

Definition at line 762 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_USTAT, ASSERT, and HWREG.

| void ADCSequenceUnderflowClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum | ||

| ) |

Clears the underflow condition on a sample sequence.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

This function clears an underflow condition on one of the sample sequencers. The underflow condition must be cleared in order to detect a subsequent underflow condition (it otherwise causes no harm).

Definition at line 791 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_O_USTAT, ASSERT, and HWREG.

| void ADCSoftwareOversampleConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t | ui32Factor | ||

| ) |

Configures the software oversampling factor of the ADC.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| ui32Factor | is the number of samples to be averaged. |

This function configures the software oversampling for the ADC, which can be used to provide better resolution on the sampled data. Oversampling is accomplished by averaging multiple samples from the same analog input. Three different oversampling rates are supported; 2x, 4x, and 8x.

Oversampling is only supported on the sample sequencers that are more than one sample in depth (that is, the fourth sample sequencer is not supported). Oversampling by 2x (for example) divides the depth of the sample sequencer by two; so 2x oversampling on the first sample sequencer can only provide four samples per trigger. This also means that 8x oversampling is only available on the first sample sequencer.

Definition at line 923 of file adc.c.

References ADC0_BASE, ADC1_BASE, ASSERT, and g_pui8OversampleFactor.

| void ADCSoftwareOversampleDataGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t * | pui32Buffer, | ||

| uint32_t | ui32Count | ||

| ) |

Gets the captured data for a sample sequence using software oversampling.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| pui32Buffer | is the address where the data is stored. |

| ui32Count | is the number of samples to be read. |

This function copies data from the specified sample sequence output FIFO to a memory resident buffer with software oversampling applied. The requested number of samples are copied into the data buffer; if there are not enough samples in the hardware FIFO to satisfy this many oversampled data items, then incorrect results are returned. It is the caller's responsibility to read only the samples that are available and wait until enough data is available, for example as a result of receiving an interrupt.

Definition at line 1053 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_SEQ, ADC_SEQ_STEP, ADC_SSFIFO, ASSERT, g_pui8OversampleFactor, and HWREG.

| void ADCSoftwareOversampleStepConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32SequenceNum, | ||

| uint32_t | ui32Step, | ||

| uint32_t | ui32Config | ||

| ) |

Configures a step of the software oversampled sequencer.

| ui32Base | is the base address of the ADC module. |

| ui32SequenceNum | is the sample sequence number. |

| ui32Step | is the step to be configured. |

| ui32Config | is the configuration of this step. |

This function configures a step of the sample sequencer when using the software oversampling feature. The number of steps available depends on the oversampling factor set by ADCSoftwareOversampleConfigure(). The value of ui32Config is the same as defined for ADCSequenceStepConfigure().

Definition at line 968 of file adc.c.

References ADC0_BASE, ADC1_BASE, ADC_SEQ, ADC_SEQ_STEP, ADC_SSCTL, ADC_SSCTL0_END0, ADC_SSCTL0_IE0, ADC_SSEMUX, ADC_SSMUX, ASSERT, g_pui8OversampleFactor, and HWREG.

|

static |

Definition at line 81 of file adc.c.

Referenced by ADCSoftwareOversampleConfigure(), ADCSoftwareOversampleDataGet(), and ADCSoftwareOversampleStepConfigure().