|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Macros | |

| #define | EPI_HB8_CS_MASK |

| #define | EPI_HB16_CS_MASK (EPI_HB8_CS_MASK | EPI_HB16_BURST_TRAFFIC) |

Functions | |

| void | EPIWorkaroundWordWrite (uint32_t *pui32Addr, uint32_t ui32Value) |

| uint32_t | EPIWorkaroundWordRead (uint32_t *pui32Addr) |

| void | EPIWorkaroundHWordWrite (uint16_t *pui16Addr, uint16_t ui16Value) |

| uint16_t | EPIWorkaroundHWordRead (uint16_t *pui16Addr) |

| void | EPIWorkaroundByteWrite (uint8_t *pui8Addr, uint8_t ui8Value) |

| uint8_t | EPIWorkaroundByteRead (uint8_t *pui8Addr) |

| void | EPIModeSet (uint32_t ui32Base, uint32_t ui32Mode) |

| void | EPIDividerSet (uint32_t ui32Base, uint32_t ui32Divider) |

| void | EPIDividerCSSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32Divider) |

| void | EPIDMATxCount (uint32_t ui32Base, uint32_t ui32Count) |

| void | EPIConfigSDRAMSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32Refresh) |

| void | EPIConfigHB8Set (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32MaxWait) |

| void | EPIConfigHB16Set (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32MaxWait) |

| void | EPIConfigHB8CSSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32Config) |

| void | EPIConfigHB16CSSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32Config) |

| void | EPIConfigHB8TimingSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32Config) |

| void | EPIConfigHB16TimingSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32Config) |

| void | EPIPSRAMConfigRegSet (uint32_t ui32Base, uint32_t ui32CS, uint32_t ui32CR) |

| void | EPIPSRAMConfigRegRead (uint32_t ui32Base, uint32_t ui32CS) |

| bool | EPIPSRAMConfigRegGetNonBlocking (uint32_t ui32Base, uint32_t ui32CS, uint32_t *pui32CR) |

| uint32_t | EPIPSRAMConfigRegGet (uint32_t ui32Base, uint32_t ui32CS) |

| void | EPIConfigGPModeSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32FrameCount, uint32_t ui32MaxWait) |

| void | EPIAddressMapSet (uint32_t ui32Base, uint32_t ui32Map) |

| void | EPINonBlockingReadConfigure (uint32_t ui32Base, uint32_t ui32Channel, uint32_t ui32DataSize, uint32_t ui32Address) |

| void | EPINonBlockingReadStart (uint32_t ui32Base, uint32_t ui32Channel, uint32_t ui32Count) |

| void | EPINonBlockingReadStop (uint32_t ui32Base, uint32_t ui32Channel) |

| uint32_t | EPINonBlockingReadCount (uint32_t ui32Base, uint32_t ui32Channel) |

| uint32_t | EPINonBlockingReadAvail (uint32_t ui32Base) |

| uint32_t | EPINonBlockingReadGet32 (uint32_t ui32Base, uint32_t ui32Count, uint32_t *pui32Buf) |

| uint32_t | EPINonBlockingReadGet16 (uint32_t ui32Base, uint32_t ui32Count, uint16_t *pui16Buf) |

| uint32_t | EPINonBlockingReadGet8 (uint32_t ui32Base, uint32_t ui32Count, uint8_t *pui8Buf) |

| void | EPIFIFOConfig (uint32_t ui32Base, uint32_t ui32Config) |

| uint32_t | EPIWriteFIFOCountGet (uint32_t ui32Base) |

| void | EPIIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | EPIIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| uint32_t | EPIIntStatus (uint32_t ui32Base, bool bMasked) |

| uint32_t | EPIIntErrorStatus (uint32_t ui32Base) |

| void | EPIIntErrorClear (uint32_t ui32Base, uint32_t ui32ErrFlags) |

| static uint32_t | _EPIIntNumberGet (uint32_t ui32Base) |

| void | EPIIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | EPIIntUnregister (uint32_t ui32Base) |

| #define EPI_HB16_CS_MASK (EPI_HB8_CS_MASK | EPI_HB16_BURST_TRAFFIC) |

Definition at line 67 of file epi.c.

Referenced by EPIConfigHB16CSSet().

| #define EPI_HB8_CS_MASK |

|

static |

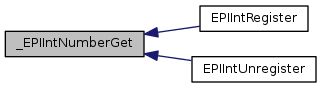

Returns the interrupt number for a given EPI base address.

| ui32Base | is the base address of the EPI module. |

This function returns the interrupt number for the EPI module with the base address passed in the ui32Base parameter.

Definition at line 2070 of file epi.c.

References ASSERT, CLASS_IS_TM4C129, EPI0_BASE, and INT_EPI0_TM4C129.

Referenced by EPIIntRegister(), and EPIIntUnregister().

| void EPIAddressMapSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Map | ||

| ) |

Configures the address map for the external interface.

| ui32Base | is the EPI module base address. |

| ui32Map | is the address mapping configuration. |

This function is used to configure the address mapping for the external interface, which then determines the base address of the external memory or device within the processor peripheral and/or memory space.

The parameter ui32Map is the logical OR of the following:

Definition at line 1415 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_ADDRMAP, and HWREG.

| void EPIConfigGPModeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32FrameCount, | ||

| uint32_t | ui32MaxWait | ||

| ) |

Configures the interface for general-purpose mode operation.

| ui32Base | is the EPI module base address. |

| ui32Config | is the interface configuration. |

| ui32FrameCount | is the frame size in clocks, if the frame signal is used (0-15). |

| ui32MaxWait | is currently not used. |

This function is used to configure the interface when used in general-purpose operation as chosen with the function EPIModeSet(). The parameter ui32Config is the logical OR of the following:

The parameter ui32FrameCount is the number of clocks used to form the framing signal, if the framing signal is used. The behavior depends on whether the frame signal is a pulse or a 50/50 duty cycle.

Definition at line 1335 of file epi.c.

References ASSERT, EPI0_BASE, EPI_GPCFG_FRMCNT_M, EPI_GPCFG_FRMCNT_S, EPI_O_GPCFG, and HWREG.

| void EPIConfigHB16CSSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32Config | ||

| ) |

Sets the individual chip select configuration for the Host-bus 16 interface.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select value to configure. |

| ui32Config | is the configuration settings. |

This function is used to configure individual chip select settings for the Host-bus 16 interface mode. EPIConfigHB16Set() must have been set up with the EPI_HB16_CSBAUD flag for the individual chip select configuration option to be available.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The parameter ui32Config is the logical OR the following:

Definition at line 877 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16_CS_MASK, EPI_O_HB16CFG, EPI_O_HB16CFG3, and HWREG.

| void EPIConfigHB16Set | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32MaxWait | ||

| ) |

Configures the interface for Host-bus 16 operation.

| ui32Base | is the EPI module base address. |

| ui32Config | is the interface configuration. |

| ui32MaxWait | is the maximum number of external clocks to wait if a FIFO ready signal is holding off the transaction. |

This function is used to configure the interface when used in Host-bus 16 operation as chosen with the function EPIModeSet(). The parameter ui32Config is the logical OR of the following:

In addition, some parts support CS2n and CS3n for a total of 4 chip selects. If EPI_HB16_CSBAUD is configured, EPIDividerCSSet() should be used to to configure the divider for CS2n and CS3n. They both also use the lower 16 bits passed to EPIDividerSet() if this option is absent.

The use of EPI_HB16_CSBAUD also allows for unique chip select configurations. CS0n, CS1n, CS2n, and CS3n can each be configured by calling EPIConfigHB16CSSet() if EPI_HB16_CSBAUD is used. Otherwise, the configuration provided in ui32Config is used for all chip selects.

Definition at line 712 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16_CSBAUD, EPI_HB16_CSCFG_MASK, EPI_HB16CFG2_CSBAUD, EPI_HB16CFG_MAXWAIT_M, EPI_HB16CFG_MAXWAIT_S, EPI_O_HB16CFG, EPI_O_HB16CFG2, and HWREG.

| void EPIConfigHB16TimingSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32Config | ||

| ) |

Sets the individual chip select timing settings for the Host-bus 16 interface.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select value to configure. |

| ui32Config | is the configuration settings. |

This function is used to set individual chip select timings for the Host-bus 16 interface mode.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The parameter ui32Config is the logical OR of the following:

Definition at line 1033 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_HB16TIME, and HWREG.

| void EPIConfigHB8CSSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32Config | ||

| ) |

Sets the individual chip select configuration for the Host-bus 8 interface.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select value to configure. |

| ui32Config | is the configuration settings. |

This function is used to configure individual chip select settings for the Host-bus 8 interface mode. EPIConfigHB8Set() must have been setup with the EPI_HB8_CSBAUD flag for the individual chip select configuration option to be available.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The parameter ui32Config is the logical OR of the following:

Definition at line 790 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB8_CS_MASK, EPI_O_HB8CFG, EPI_O_HB8CFG3, and HWREG.

| void EPIConfigHB8Set | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32MaxWait | ||

| ) |

Configures the interface for Host-bus 8 operation.

| ui32Base | is the EPI module base address. |

| ui32Config | is the interface configuration. |

| ui32MaxWait | is the maximum number of external clocks to wait if a FIFO ready signal is holding off the transaction, 0-255. |

This function is used to configure the interface when used in host-bus 8 operation as chosen with the function EPIModeSet(). The parameter ui32Config is the logical OR of the following:

In addition, some parts support CS2n and CS3n for a total of 4 chip selects. If EPI_HB8_CSBAUD is configured, EPIDividerCSSet() should be used to to configure the divider for CS2n and CS3n. They both also use the lower 16 bits passed to EPIDividerSet() if this option is absent.

The use of EPI_HB8_CSBAUD also allows for unique chip select configurations. CS0n, CS1n, CS2n, and CS3n can each be configured by calling EPIConfigHB8CSSet() if EPI_HB8_CSBAUD is used. Otherwise, the configuration provided in ui32Config is used for all chip selects enabled.

Definition at line 569 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB8_CSBAUD, EPI_HB8_CSCFG_MASK, EPI_HB8CFG2_CSBAUD, EPI_HB8CFG_MAXWAIT_M, EPI_HB8CFG_MAXWAIT_S, EPI_O_HB8CFG, EPI_O_HB8CFG2, and HWREG.

| void EPIConfigHB8TimingSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32Config | ||

| ) |

Sets the individual chip select timing settings for the Host-bus 8 interface.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select value to configure. |

| ui32Config | is the configuration settings. |

This function is used to set individual chip select timings for the Host-bus 8 interface mode.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The parameter ui32Config is the logical OR of the following:

Definition at line 958 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_HB8TIME, and HWREG.

| void EPIConfigSDRAMSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32Refresh | ||

| ) |

Configures the SDRAM mode of operation.

| ui32Base | is the EPI module base address. |

| ui32Config | is the SDRAM interface configuration. |

| ui32Refresh | is the refresh count in core clocks (0-2047). |

This function is used to configure the SDRAM interface, when the SDRAM mode is chosen with the function EPIModeSet(). The parameter ui32Config is the logical OR of several sets of choices:

The processor core frequency must be specified with one of the following:

The low power mode is specified with one of the following:

The SDRAM device size is specified with one of the following:

The parameter ui16Refresh sets the refresh counter in units of core clock ticks. It is an 11-bit value with a range of 0 - 2047 counts.

Definition at line 444 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_SDRAMCFG, EPI_SDRAMCFG_RFSH_M, EPI_SDRAMCFG_RFSH_S, and HWREG.

| void EPIDividerCSSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32Divider | ||

| ) |

Sets the clock divider for the specified CS in the EPI module.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select to modify and has a valid range of 0-3. |

| ui32Divider | is the value of the clock divider to be applied to the external interface (0-65535). |

This function sets the clock divider(s) for the specified CS that is used to determine the clock rate of the external interface. The ui32Divider value is used to derive the EPI clock rate from the system clock based on the following formula.

EPIClk = (Divider == 0) ? SysClk : (SysClk / (((Divider / 2) + 1) * 2))

For example, a divider value of 1 results in an EPI clock rate of half the system clock, value of 2 or 3 yields one quarter of the system clock and a value of 4 results in one sixth of the system clock rate.

Definition at line 339 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_BAUD, EPI_O_BAUD2, and HWREG.

| void EPIDividerSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Divider | ||

| ) |

Sets the clock divider for the EPI module's CS0n/CS1n.

| ui32Base | is the EPI module base address. |

| ui32Divider | is the value of the clock divider to be applied to the external interface (0-65535). |

This function sets the clock divider(s) that is used to determine the clock rate of the external interface. The ui32Divider value is used to derive the EPI clock rate from the system clock based on the following formula.

EPIClk = (Divider == 0) ? SysClk : (SysClk / (((Divider / 2) + 1) * 2))

For example, a divider value of 1 results in an EPI clock rate of half the system clock, value of 2 or 3 yields one quarter of the system clock and a value of 4 results in one sixth of the system clock rate.

In cases where a dual chip select mode is in use and different clock rates are required for each chip select, the ui32Divider parameter must contain two dividers. The lower 16 bits define the divider to be used with CS0n and the upper 16 bits define the divider for CS1n.

Definition at line 298 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_BAUD, and HWREG.

| void EPIDMATxCount | ( | uint32_t | ui32Base, |

| uint32_t | ui32Count | ||

| ) |

Sets the transfer count for uDMA transmit operations on EPI.

| ui32Base | is the EPI module base address. |

| ui32Count | is the number of units to transmit by uDMA to WRFIFO. |

This function is used to help configure the EPI uDMA transmit operations. A non-zero transmit count in combination with a FIFO threshold trigger asserts an EPI uDMA transmit.

Note that, although the EPI peripheral can handle counts of up to 65535, a single uDMA transfer has a maximum length of 1024 units so ui32Count should be set to values less than or equal to 1024.

Definition at line 391 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_DMATXCNT, and HWREG.

| void EPIFIFOConfig | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the read FIFO.

| ui32Base | is the EPI module base address. |

| ui32Config | is the FIFO configuration. |

This function configures the FIFO trigger levels and error generation. The parameter ui32Config is the logical OR of the following:

Definition at line 1830 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_FIFOLVL, and HWREG.

| void EPIIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables EPI interrupt sources.

| ui32Base | is the EPI module base address. |

| ui32IntFlags | is a bit mask of the interrupt sources to be disabled. |

This function disables the specified EPI sources for interrupt generation. The ui32IntFlags parameter can be the logical OR of any of the following values:

Definition at line 1927 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_IM, and HWREG.

| void EPIIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables EPI interrupt sources.

| ui32Base | is the EPI module base address. |

| ui32IntFlags | is a bit mask of the interrupt sources to be enabled. |

This function enables the specified EPI sources to generate interrupts. The ui32IntFlags parameter can be the logical OR of any of the following values:

Definition at line 1892 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_IM, and HWREG.

| void EPIIntErrorClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32ErrFlags | ||

| ) |

Clears pending EPI error sources.

| ui32Base | is the EPI module base address. |

| ui32ErrFlags | is a bit mask of the error sources to be cleared. |

This function clears the specified pending EPI errors. The ui32ErrFlags parameter can be the logical OR of any of the following values:

Definition at line 2042 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_EISC, and HWREG.

| uint32_t EPIIntErrorStatus | ( | uint32_t | ui32Base | ) |

Gets the EPI error interrupt status.

| ui32Base | is the EPI module base address. |

This function returns the error status of the EPI. If the return value of the function EPIIntStatus() has the flag EPI_INT_ERR set, then this function can be used to determine the cause of the error.

Definition at line 2005 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_EISC, and HWREG.

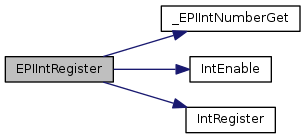

| void EPIIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the EPI module.

| ui32Base | is the EPI module base address. |

| pfnHandler | is a pointer to the function to be called when the interrupt is activated. |

This sets and enables the handler to be called when the EPI module generates an interrupt. Specific EPI interrupts must still be enabled with the EPIIntEnable() function.

Definition at line 2111 of file epi.c.

References _EPIIntNumberGet(), ASSERT, EPI0_BASE, IntEnable(), and IntRegister().

| uint32_t EPIIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the EPI interrupt status.

| ui32Base | is the EPI module base address. |

| bMasked | is set true to get the masked interrupt status, or false to get the raw interrupt status. |

This function returns the EPI interrupt status. It can return either the raw or masked interrupt status.

Definition at line 1963 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_MIS, EPI_O_RIS, and HWREG.

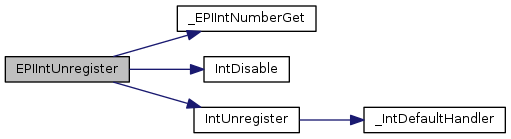

| void EPIIntUnregister | ( | uint32_t | ui32Base | ) |

Removes a registered interrupt handler for the EPI module.

| ui32Base | is the EPI module base address. |

This function disables and clears the handler to be called when the EPI interrupt occurs.

Definition at line 2155 of file epi.c.

References _EPIIntNumberGet(), ASSERT, EPI0_BASE, IntDisable(), and IntUnregister().

| void EPIModeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Mode | ||

| ) |

Sets the usage mode of the EPI module.

| ui32Base | is the EPI module base address. |

| ui32Mode | is the usage mode of the EPI module. |

This functions sets the operating mode of the EPI module. The parameter ui32Mode must be one of the following:

Selection of any of the above modes enables the EPI module, except for EPI_MODE_DISABLE, which is used to disable the module.

Definition at line 252 of file epi.c.

References ASSERT, EPI0_BASE, EPI_MODE_DISABLE, EPI_MODE_GENERAL, EPI_MODE_HB16, EPI_MODE_HB8, EPI_MODE_SDRAM, EPI_O_CFG, and HWREG.

| uint32_t EPINonBlockingReadAvail | ( | uint32_t | ui32Base | ) |

Get the count of items available in the read FIFO.

| ui32Base | is the EPI module base address. |

This function gets the number of items that are available to read in the read FIFO. The read FIFO is filled by a non-blocking read transaction which is configured by the functions EPINonBlockingReadConfigure() and EPINonBlockingReadStart().

Definition at line 1620 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_RFIFOCNT, and HWREG.

| void EPINonBlockingReadConfigure | ( | uint32_t | ui32Base, |

| uint32_t | ui32Channel, | ||

| uint32_t | ui32DataSize, | ||

| uint32_t | ui32Address | ||

| ) |

Configures a non-blocking read transaction.

| ui32Base | is the EPI module base address. |

| ui32Channel | is the read channel (0 or 1). |

| ui32DataSize | is the size of the data items to read. |

| ui32Address | is the starting address to read. |

This function is used to configure a non-blocking read channel for a transaction. Two channels are available that can be used in a ping-pong method for continuous reading. It is not necessary to use both channels to perform a non-blocking read.

The parameter ui8DataSize is one of EPI_NBCONFIG_SIZE_8, EPI_NBCONFIG_SIZE_16, or EPI_NBCONFIG_SIZE_32 for 8-bit, 16-bit, or 32-bit sized data transfers.

The parameter ui32Address is the starting address for the read, relative to the external device. The start of the device is address 0.

Once configured, the non-blocking read is started by calling EPINonBlockingReadStart(). If the addresses to be read from the device are in a sequence, it is not necessary to call this function multiple times. Until it is changed, the EPI module stores the last address that was used for a non-blocking read (per channel).

Definition at line 1460 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_RADDR0, EPI_O_RSIZE0, EPI_O_RSIZE1, and HWREG.

| uint32_t EPINonBlockingReadCount | ( | uint32_t | ui32Base, |

| uint32_t | ui32Channel | ||

| ) |

Get the count remaining for a non-blocking transaction.

| ui32Base | is the EPI module base address. |

| ui32Channel | is the read channel (0 or 1). |

This function gets the remaining count of items for a non-blocking read transaction.

Definition at line 1584 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_RPSTD0, EPI_O_RPSTD1, and HWREG.

| uint32_t EPINonBlockingReadGet16 | ( | uint32_t | ui32Base, |

| uint32_t | ui32Count, | ||

| uint16_t * | pui16Buf | ||

| ) |

Read available data from the read FIFO, as 16-bit data items.

| ui32Base | is the EPI module base address. |

| ui32Count | is the maximum count of items to read. |

| pui16Buf | is the caller-supplied buffer where the read data is stored. |

This function reads 16-bit data items from the read FIFO and stores the values in a caller-supplied buffer. The function reads and stores data from the FIFO until there is no more data in the FIFO or the maximum count is reached as specified in the parameter ui32Count. The actual count of items is returned.

Definition at line 1707 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_READFIFO0, EPI_O_RFIFOCNT, and HWREG.

| uint32_t EPINonBlockingReadGet32 | ( | uint32_t | ui32Base, |

| uint32_t | ui32Count, | ||

| uint32_t * | pui32Buf | ||

| ) |

Read available data from the read FIFO, as 32-bit data items.

| ui32Base | is the EPI module base address. |

| ui32Count | is the maximum count of items to read. |

| pui32Buf | is the caller supplied buffer where the read data is stored. |

This function reads 32-bit data items from the read FIFO and stores the values in a caller-supplied buffer. The function reads and stores data from the FIFO until there is no more data in the FIFO or the maximum count is reached as specified in the parameter ui32Count. The actual count of items is returned.

Definition at line 1652 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_READFIFO0, EPI_O_RFIFOCNT, and HWREG.

| uint32_t EPINonBlockingReadGet8 | ( | uint32_t | ui32Base, |

| uint32_t | ui32Count, | ||

| uint8_t * | pui8Buf | ||

| ) |

Read available data from the read FIFO, as 8-bit data items.

| ui32Base | is the EPI module base address. |

| ui32Count | is the maximum count of items to read. |

| pui8Buf | is the caller-supplied buffer where the read data is stored. |

This function reads 8-bit data items from the read FIFO and stores the values in a caller-supplied buffer. The function reads and stores data from the FIFO until there is no more data in the FIFO or the maximum count is reached as specified in the parameter ui32Count. The actual count of items is returned.

Definition at line 1762 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_READFIFO0, EPI_O_RFIFOCNT, and HWREG.

| void EPINonBlockingReadStart | ( | uint32_t | ui32Base, |

| uint32_t | ui32Channel, | ||

| uint32_t | ui32Count | ||

| ) |

Starts a non-blocking read transaction.

| ui32Base | is the EPI module base address. |

| ui32Channel | is the read channel (0 or 1). |

| ui32Count | is the number of items to read (1-4095). |

This function starts a non-blocking read that was previously configured with the function EPINonBlockingReadConfigure(). Once this function is called, the EPI module begins reading data from the external device into the read FIFO. The EPI stops reading when the FIFO fills up and resumes reading when the application drains the FIFO, until the total specified count of data items has been read.

Once a read transaction is completed and the FIFO drained, another transaction can be started from the next address by calling this function again.

Definition at line 1512 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_RPSTD0, EPI_O_RPSTD1, and HWREG.

| void EPINonBlockingReadStop | ( | uint32_t | ui32Base, |

| uint32_t | ui32Channel | ||

| ) |

Stops a non-blocking read transaction.

| ui32Base | is the EPI module base address. |

| ui32Channel | is the read channel (0 or 1). |

This function cancels a non-blocking read transaction that is already in progress.

Definition at line 1549 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_RPSTD0, EPI_O_RPSTD1, and HWREG.

| uint32_t EPIPSRAMConfigRegGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS | ||

| ) |

Retrieves the contents of the EPI PSRAM configuration register.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select target. |

This function retrieves the EPI PSRAM configuration register. The register is read once the EPI PSRAM configuration register read enable signal is de-asserted.

The Host-bus 16 interface mode should be set up and EPIPSRAMConfigRegRead() should be called prior to calling this function.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3.

Definition at line 1258 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16CFG_RDCRE, EPI_O_HB16CFG, EPI_O_HB16CFG3, EPI_O_HBPSRAM, and HWREG.

| bool EPIPSRAMConfigRegGetNonBlocking | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t * | pui32CR | ||

| ) |

Retrieves the contents of the EPI PSRAM configuration register.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select target. |

| pui32CR | is the provided storage used to hold the register value. |

This function copies the contents of the EPI PSRAM configuration register to the provided storage if the PSRAM read configuration register enable is no longer asserted. Otherwise the provided storage is not modified.

The Host-bus 16 interface mode should be set up and EPIPSRAMConfigRegRead() should be called prior to calling this function.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The pui32CR parameter is a pointer to provided storage used to hold the register value.

Definition at line 1188 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16CFG_RDCRE, EPI_O_HB16CFG, EPI_O_HB16CFG3, EPI_O_HBPSRAM, and HWREG.

| void EPIPSRAMConfigRegRead | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS | ||

| ) |

Requests a configuration register read from the PSRAM.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select target. |

This function requests a read of the PSRAM's configuration register. The Host-bus 16 interface mode should be configured prior to calling this function. The EPIPSRAMConfigRegGet() and EPIPSRAMConfigRegGetNonBlocking() can be used to retrieve the configuration register value.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3.

Definition at line 1131 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16CFG_RDCRE, EPI_O_HB16CFG, EPI_O_HB16CFG3, and HWREG.

| void EPIPSRAMConfigRegSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint32_t | ui32CR | ||

| ) |

Sets the PSRAM configuration register.

| ui32Base | is the EPI module base address. |

| ui32CS | is the chip select target. |

| ui32CR | is the PSRAM configuration register value. |

This function sets the PSRAM's configuration register by using the PSRAM configuration register enable signal. The Host-bus 16 interface mode should be configured prior to calling this function.

The ui32Base parameter is the base address for the EPI hardware module. The ui32CS parameter specifies the chip select to configure and has a valid range of 0-3. The parameter ui32CR value is determined by consulting the PSRAM's data sheet.

Definition at line 1072 of file epi.c.

References ASSERT, EPI0_BASE, EPI_HB16CFG_WRCRE, EPI_O_HB16CFG, EPI_O_HB16CFG3, EPI_O_HBPSRAM, and HWREG.

| uint8_t EPIWorkaroundByteRead | ( | uint8_t * | pui8Addr | ) |

Safely reads a byte from the EPI 0x10000000 address space.

| pui8Addr | is the address which is to be read. |

This function must be used when reading bytes from EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| void EPIWorkaroundByteWrite | ( | uint8_t * | pui8Addr, |

| uint8_t | ui8Value | ||

| ) |

Safely writes a byte to the EPI 0x10000000 address space.

| pui8Addr | is the address which is to be written. |

| ui8Value | is the 8-bit byte to write. |

This function must be used when writing bytes to EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| uint16_t EPIWorkaroundHWordRead | ( | uint16_t * | pui16Addr | ) |

Safely reads a half-word from the EPI 0x10000000 address space.

| pui16Addr | is the address which is to be read. |

This function must be used when reading half-words from EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| void EPIWorkaroundHWordWrite | ( | uint16_t * | pui16Addr, |

| uint16_t | ui16Value | ||

| ) |

Safely writes a half-word to the EPI 0x10000000 address space.

| pui16Addr | is the address which is to be written. |

| ui16Value | is the 16-bit half-word to write. |

This function must be used when writing half-words to EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| uint32_t EPIWorkaroundWordRead | ( | uint32_t * | pui32Addr | ) |

Safely reads a word from the EPI 0x10000000 address space.

| pui32Addr | is the address which is to be read. |

This function must be used when reading words from EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| void EPIWorkaroundWordWrite | ( | uint32_t * | pui32Addr, |

| uint32_t | ui32Value | ||

| ) |

Safely writes a word to the EPI 0x10000000 address space.

| pui32Addr | is the address which is to be written. |

| ui32Value | is the 32-bit word to write. |

This function must be used when writing words to EPI-attached memory configured to use the address space at 0x10000000 on devices affected by the EPI#01 erratum. Direct access to memory in these cases can cause data corruption depending upon memory accesses immediately before or after the EPI access but using this function will allow EPI accesses to complete correctly. The function is defined as ``inline'' in epi.h.

Use of this function on a device not affected by the erratum is safe but will impact performance due to an additional overhead of at least 2 cycles per access. This erratum affects only the 0x10000000 address space typically used to store the LCD controller frame buffer. The 0x60000000 address space is not affected and applications using this address mapping need not use this function.

| uint32_t EPIWriteFIFOCountGet | ( | uint32_t | ui32Base | ) |

Reads the number of empty slots in the write transaction FIFO.

| ui32Base | is the EPI module base address. |

This function returns the number of slots available in the transaction FIFO. It can be used in a polling method to avoid attempting a write that would stall.

Definition at line 1858 of file epi.c.

References ASSERT, EPI0_BASE, EPI_O_WFIFOCNT, and HWREG.