|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Functions | |

| static uint32_t | _I2CIntNumberGet (uint32_t ui32Base) |

| void | I2CMasterInitExpClk (uint32_t ui32Base, uint32_t ui32I2CClk, bool bFast) |

| void | I2CSlaveInit (uint32_t ui32Base, uint8_t ui8SlaveAddr) |

| void | I2CSlaveAddressSet (uint32_t ui32Base, uint8_t ui8AddrNum, uint8_t ui8SlaveAddr) |

| void | I2CMasterEnable (uint32_t ui32Base) |

| void | I2CSlaveEnable (uint32_t ui32Base) |

| void | I2CMasterDisable (uint32_t ui32Base) |

| void | I2CSlaveDisable (uint32_t ui32Base) |

| void | I2CIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | I2CIntUnregister (uint32_t ui32Base) |

| void | I2CMasterIntEnable (uint32_t ui32Base) |

| void | I2CMasterIntEnableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | I2CSlaveIntEnable (uint32_t ui32Base) |

| void | I2CSlaveIntEnableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | I2CMasterIntDisable (uint32_t ui32Base) |

| void | I2CMasterIntDisableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | I2CSlaveIntDisable (uint32_t ui32Base) |

| void | I2CSlaveIntDisableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| bool | I2CMasterIntStatus (uint32_t ui32Base, bool bMasked) |

| uint32_t | I2CMasterIntStatusEx (uint32_t ui32Base, bool bMasked) |

| bool | I2CSlaveIntStatus (uint32_t ui32Base, bool bMasked) |

| uint32_t | I2CSlaveIntStatusEx (uint32_t ui32Base, bool bMasked) |

| void | I2CMasterIntClear (uint32_t ui32Base) |

| void | I2CMasterIntClearEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | I2CSlaveIntClear (uint32_t ui32Base) |

| void | I2CSlaveIntClearEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | I2CMasterSlaveAddrSet (uint32_t ui32Base, uint8_t ui8SlaveAddr, bool bReceive) |

| uint32_t | I2CMasterLineStateGet (uint32_t ui32Base) |

| bool | I2CMasterBusy (uint32_t ui32Base) |

| bool | I2CMasterBusBusy (uint32_t ui32Base) |

| void | I2CMasterControl (uint32_t ui32Base, uint32_t ui32Cmd) |

| uint32_t | I2CMasterErr (uint32_t ui32Base) |

| void | I2CMasterDataPut (uint32_t ui32Base, uint8_t ui8Data) |

| uint32_t | I2CMasterDataGet (uint32_t ui32Base) |

| void | I2CMasterTimeoutSet (uint32_t ui32Base, uint32_t ui32Value) |

| void | I2CSlaveACKOverride (uint32_t ui32Base, bool bEnable) |

| void | I2CSlaveACKValueSet (uint32_t ui32Base, bool bACK) |

| uint32_t | I2CSlaveStatus (uint32_t ui32Base) |

| void | I2CSlaveDataPut (uint32_t ui32Base, uint8_t ui8Data) |

| uint32_t | I2CSlaveDataGet (uint32_t ui32Base) |

| void | I2CTxFIFOConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | I2CTxFIFOFlush (uint32_t ui32Base) |

| void | I2CRxFIFOConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | I2CRxFIFOFlush (uint32_t ui32Base) |

| uint32_t | I2CFIFOStatus (uint32_t ui32Base) |

| void | I2CFIFODataPut (uint32_t ui32Base, uint8_t ui8Data) |

| uint32_t | I2CFIFODataPutNonBlocking (uint32_t ui32Base, uint8_t ui8Data) |

| uint32_t | I2CFIFODataGet (uint32_t ui32Base) |

| uint32_t | I2CFIFODataGetNonBlocking (uint32_t ui32Base, uint8_t *pui8Data) |

| void | I2CMasterBurstLengthSet (uint32_t ui32Base, uint8_t ui8Length) |

| uint32_t | I2CMasterBurstCountGet (uint32_t ui32Base) |

| void | I2CMasterGlitchFilterConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | I2CSlaveFIFOEnable (uint32_t ui32Base, uint32_t ui32Config) |

| void | I2CSlaveFIFODisable (uint32_t ui32Base) |

Variables | |

| static const uint32_t | g_ppui32I2CIntMap [][2] |

| static const int_fast8_t | g_i8I2CIntMapRows |

| static const uint32_t | g_ppui32I2CIntMapSnowflake [][2] |

| static const int_fast8_t | g_i8I2CIntMapSnowflakeRows |

|

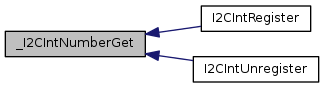

static |

Definition at line 131 of file i2c.c.

References ASSERT, CLASS_IS_TM4C129, g_i8I2CIntMapRows, g_i8I2CIntMapSnowflakeRows, g_ppui32I2CIntMap, and g_ppui32I2CIntMapSnowflake.

Referenced by I2CIntRegister(), and I2CIntUnregister().

| uint32_t I2CFIFODataGet | ( | uint32_t | ui32Base | ) |

Reads a byte from the I2C receive FIFO.

| ui32Base | is the base address of the I2C module. |

This function reads a byte of data from I2C receive FIFO and places it in the location specified by the pui8Data parameter. If there is no data available, this function waits until data is received before returning.

Definition at line 1901 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOSTATUS_RXFE, I2C_O_FIFODATA, and I2C_O_FIFOSTATUS.

| uint32_t I2CFIFODataGetNonBlocking | ( | uint32_t | ui32Base, |

| uint8_t * | pui8Data | ||

| ) |

Reads a byte from the I2C receive FIFO.

| ui32Base | is the base address of the I2C module. |

| pui8Data | is a pointer where the read data is stored. |

This function reads a byte of data from I2C receive FIFO and places it in the location specified by the pui8Data parameter. If there is no data available, this functions returns 0.

Definition at line 1939 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOSTATUS_RXFE, I2C_O_FIFODATA, and I2C_O_FIFOSTATUS.

| void I2CFIFODataPut | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Writes a data byte to the I2C transmit FIFO.

| ui32Base | is the base address of the I2C module. |

| ui8Data | is the data to be placed into the transmit FIFO. |

This function adds a byte of data to the I2C transmit FIFO. If there is no space available in the FIFO, this function waits for space to become available before returning.

Definition at line 1826 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOSTATUS_TXFF, I2C_O_FIFODATA, and I2C_O_FIFOSTATUS.

| uint32_t I2CFIFODataPutNonBlocking | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Writes a data byte to the I2C transmit FIFO.

| ui32Base | is the base address of the I2C module. |

| ui8Data | is the data to be placed into the transmit FIFO. |

This function adds a byte of data to the I2C transmit FIFO. If there is no space available in the FIFO, this function returns a zero.

Definition at line 1863 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOSTATUS_TXFF, I2C_O_FIFODATA, and I2C_O_FIFOSTATUS.

| uint32_t I2CFIFOStatus | ( | uint32_t | ui32Base | ) |

Gets the current FIFO status.

| ui32Base | is the base address of the I2C module. |

This function retrieves the status for both the transmit (TX) and receive (RX) FIFOs. The trigger level for the transmit FIFO is set using I2CTxFIFOConfigSet() and for the receive FIFO using I2CTxFIFOConfigSet().

Definition at line 1795 of file i2c.c.

References ASSERT, HWREG, and I2C_O_FIFOSTATUS.

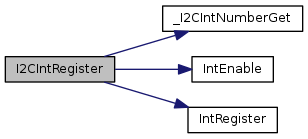

| void I2CIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the I2C module.

| ui32Base | is the base address of the I2C module. |

| pfnHandler | is a pointer to the function to be called when the I2C interrupt occurs. |

This function sets the handler to be called when an I2C interrupt occurs. This function enables the global interrupt in the interrupt controller; specific I2C interrupts must be enabled via I2CMasterIntEnable() and I2CSlaveIntEnable(). If necessary, it is the interrupt handler's responsibility to clear the interrupt source via I2CMasterIntClear() and I2CSlaveIntClear().

Definition at line 473 of file i2c.c.

References _I2CIntNumberGet(), ASSERT, IntEnable(), and IntRegister().

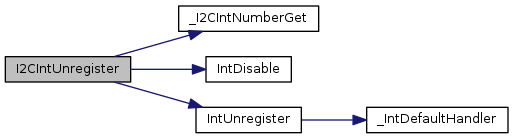

| void I2CIntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters an interrupt handler for the I2C module.

| ui32Base | is the base address of the I2C module. |

This function clears the handler to be called when an I2C interrupt occurs. This function also masks off the interrupt in the interrupt r controller so that the interrupt handler no longer is called.

Definition at line 517 of file i2c.c.

References _I2CIntNumberGet(), ASSERT, IntDisable(), and IntUnregister().

| uint32_t I2CMasterBurstCountGet | ( | uint32_t | ui32Base | ) |

Returns the current value of the burst transfer counter.

| ui32Base | is the base address of the I2C module. |

This function returns the current value of the burst transfer counter that is used by the FIFO mechanism. Software can use this value to determine how many bytes remain in a transfer, or where in the transfer the burst operation was if an error has occurred.

Definition at line 2012 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MBCNT.

| void I2CMasterBurstLengthSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8Length | ||

| ) |

Set the burst length for a I2C master FIFO operation.

| ui32Base | is the base address of the I2C module. |

| ui8Length | is the length of the burst transfer. |

This function configures the burst length for a I2C Master FIFO operation. The burst field is limited to 8 bits or 256 bytes. The burst length applies to a single I2CMCS BURST operation meaning that it specifies the burst length for only the current operation (can be TX or RX). Each burst operation must configure the burst length prior to writing the BURST bit in the I2CMCS using I2CMasterControl().

Definition at line 1981 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MBLEN.

| bool I2CMasterBusBusy | ( | uint32_t | ui32Base | ) |

Indicates whether or not the I2C bus is busy.

| ui32Base | is the base address of the I2C module. |

This function returns an indication of whether or not the I2C bus is busy. This function can be used in a multi-master environment to determine if another master is currently using the bus.

Definition at line 1222 of file i2c.c.

References ASSERT, HWREG, I2C_MCS_BUSBSY, and I2C_O_MCS.

| bool I2CMasterBusy | ( | uint32_t | ui32Base | ) |

Indicates whether or not the I2C Master is busy.

| ui32Base | is the base address of the I2C module. |

This function returns an indication of whether or not the I2C Master is busy transmitting or receiving data.

Definition at line 1187 of file i2c.c.

References ASSERT, HWREG, I2C_MCS_BUSY, and I2C_O_MCS.

| void I2CMasterControl | ( | uint32_t | ui32Base, |

| uint32_t | ui32Cmd | ||

| ) |

Controls the state of the I2C Master.

| ui32Base | is the base address of the I2C module. |

| ui32Cmd | command to be issued to the I2C Master. |

This function is used to control the state of the Master send and receive operations. The ui8Cmd parameter can be one of the following values:

Definition at line 1284 of file i2c.c.

References ASSERT, HWREG, I2C_MASTER_CMD_BURST_RECEIVE_CONT, I2C_MASTER_CMD_BURST_RECEIVE_ERROR_STOP, I2C_MASTER_CMD_BURST_RECEIVE_FINISH, I2C_MASTER_CMD_BURST_RECEIVE_START, I2C_MASTER_CMD_BURST_SEND_CONT, I2C_MASTER_CMD_BURST_SEND_ERROR_STOP, I2C_MASTER_CMD_BURST_SEND_FINISH, I2C_MASTER_CMD_BURST_SEND_START, I2C_MASTER_CMD_FIFO_BURST_RECEIVE_CONT, I2C_MASTER_CMD_FIFO_BURST_RECEIVE_ERROR_STOP, I2C_MASTER_CMD_FIFO_BURST_RECEIVE_FINISH, I2C_MASTER_CMD_FIFO_BURST_RECEIVE_START, I2C_MASTER_CMD_FIFO_BURST_SEND_CONT, I2C_MASTER_CMD_FIFO_BURST_SEND_ERROR_STOP, I2C_MASTER_CMD_FIFO_BURST_SEND_FINISH, I2C_MASTER_CMD_FIFO_BURST_SEND_START, I2C_MASTER_CMD_FIFO_SINGLE_RECEIVE, I2C_MASTER_CMD_FIFO_SINGLE_SEND, I2C_MASTER_CMD_HS_MASTER_CODE_SEND, I2C_MASTER_CMD_QUICK_COMMAND, I2C_MASTER_CMD_SINGLE_RECEIVE, I2C_MASTER_CMD_SINGLE_SEND, and I2C_O_MCS.

| uint32_t I2CMasterDataGet | ( | uint32_t | ui32Base | ) |

Receives a byte that has been sent to the I2C Master.

| ui32Base | is the base address of the I2C module. |

This function reads a byte of data from the I2C Master Data Register.

Definition at line 1409 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MDR.

| void I2CMasterDataPut | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Transmits a byte from the I2C Master.

| ui32Base | is the base address of the I2C module. |

| ui8Data | data to be transmitted from the I2C Master. |

This function places the supplied data into I2C Master Data Register.

Definition at line 1383 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MDR.

| void I2CMasterDisable | ( | uint32_t | ui32Base | ) |

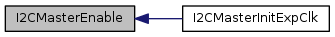

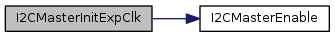

| void I2CMasterEnable | ( | uint32_t | ui32Base | ) |

Enables the I2C Master block.

| ui32Base | is the base address of the I2C module. |

This function enables operation of the I2C Master block.

Definition at line 353 of file i2c.c.

References ASSERT, HWREG, I2C_MCR_MFE, and I2C_O_MCR.

Referenced by I2CMasterInitExpClk().

| uint32_t I2CMasterErr | ( | uint32_t | ui32Base | ) |

Gets the error status of the I2C Master.

| ui32Base | is the base address of the I2C module. |

This function is used to obtain the error status of the Master send and receive operations.

Definition at line 1334 of file i2c.c.

References ASSERT, HWREG, I2C_MASTER_ERR_NONE, I2C_MCS_ADRACK, I2C_MCS_ARBLST, I2C_MCS_BUSY, I2C_MCS_DATACK, I2C_MCS_ERROR, and I2C_O_MCS.

| void I2CMasterGlitchFilterConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the I2C Master glitch filter.

| ui32Base | is the base address of the I2C module. |

| ui32Config | is the glitch filter configuration. |

This function configures the I2C Master glitch filter. The value passed in to ui32Config determines the sampling range of the glitch filter, which is configurable between 1 and 32 system clock cycles. The default configuration of the glitch filter is 0 system clock cycles, which means that it's disabled.

The ui32Config field should be any of the following values:

Definition at line 2056 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MTPR.

| void I2CMasterInitExpClk | ( | uint32_t | ui32Base, |

| uint32_t | ui32I2CClk, | ||

| bool | bFast | ||

| ) |

Initializes the I2C Master block.

| ui32Base | is the base address of the I2C module. |

| ui32I2CClk | is the rate of the clock supplied to the I2C module. |

| bFast | set up for fast data transfers. |

This function initializes operation of the I2C Master block by configuring the bus speed for the master and enabling the I2C Master block.

If the parameter bFast is true, then the master block is set up to transfer data at 400 Kbps; otherwise, it is set up to transfer data at 100 Kbps. If Fast Mode Plus (1 Mbps) is desired, software should manually write the I2CMTPR after calling this function. For High Speed (3.4 Mbps) mode, a specific command is used to switch to the faster clocks after the initial communication with the slave is done at either 100 Kbps or 400 Kbps.

The peripheral clock is the same as the processor clock. This value is returned by SysCtlClockGet(), or it can be explicitly hard coded if it is constant and known (to save the code/execution overhead of a call to SysCtlClockGet()).

Definition at line 202 of file i2c.c.

References ASSERT, HWREG, I2C_MTPR_HS, I2C_O_MTPR, I2C_O_PP, I2C_PP_HS, and I2CMasterEnable().

| void I2CMasterIntClear | ( | uint32_t | ui32Base | ) |

Clears I2C Master interrupt sources.

| ui32Base | is the base address of the I2C module. |

The I2C Master interrupt source is cleared, so that it no longer asserts. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

Definition at line 974 of file i2c.c.

References ASSERT, HWREG, I2C_MICR_IC, I2C_O_MICR, and I2C_O_MMIS.

| void I2CMasterIntClearEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears I2C Master interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. |

The specified I2C Master interrupt sources are cleared, so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

The ui32IntFlags parameter has the same definition as the ui32IntFlags parameter to I2CMasterIntEnableEx().

Definition at line 1021 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MICR.

| void I2CMasterIntDisable | ( | uint32_t | ui32Base | ) |

Disables the I2C Master interrupt.

| ui32Base | is the base address of the I2C module. |

This function disables the I2C Master interrupt source.

Definition at line 697 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MIMR.

| void I2CMasterIntDisableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables individual I2C Master interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. |

This function disables the indicated I2C Master interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter has the same definition as the ui32IntFlags parameter to I2CMasterIntEnableEx().

Definition at line 729 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MIMR.

| void I2CMasterIntEnable | ( | uint32_t | ui32Base | ) |

Enables the I2C Master interrupt.

| ui32Base | is the base address of the I2C module. |

This function enables the I2C Master interrupt source.

Definition at line 556 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MIMR.

| void I2CMasterIntEnableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables individual I2C Master interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. |

This function enables the indicated I2C Master interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 603 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MIMR.

| bool I2CMasterIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current I2C Master interrupt status.

| ui32Base | is the base address of the I2C module. |

| bMasked | is false if the raw interrupt status is requested and true if the masked interrupt status is requested. |

This function returns the interrupt status for the I2C module. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 816 of file i2c.c.

References ASSERT, HWREG, I2C_O_MMIS, and I2C_O_MRIS.

| uint32_t I2CMasterIntStatusEx | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current I2C Master interrupt status.

| ui32Base | is the base address of the I2C module. |

| bMasked | is false if the raw interrupt status is requested and true if the masked interrupt status is requested. |

This function returns the interrupt status for the I2C module. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 854 of file i2c.c.

References ASSERT, HWREG, I2C_O_MMIS, and I2C_O_MRIS.

| uint32_t I2CMasterLineStateGet | ( | uint32_t | ui32Base | ) |

Reads the state of the SDA and SCL pins.

| ui32Base | is the base address of the I2C module. |

This function returns the state of the I2C bus by providing the real time values of the SDA and SCL pins.

Definition at line 1160 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MBMON.

| void I2CMasterSlaveAddrSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8SlaveAddr, | ||

| bool | bReceive | ||

| ) |

Sets the address that the I2C Master places on the bus.

| ui32Base | is the base address of the I2C module. |

| ui8SlaveAddr | 7-bit slave address |

| bReceive | flag indicating the type of communication with the slave |

This function configures the address that the I2C Master places on the bus when initiating a transaction. When the bReceive parameter is set to true, the address indicates that the I2C Master is initiating a read from the slave; otherwise the address indicates that the I2C Master is initiating a write to the slave.

Definition at line 1128 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MSA.

| void I2CMasterTimeoutSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Value | ||

| ) |

Sets the Master clock timeout value.

| ui32Base | is the base address of the I2C module. |

| ui32Value | is the number of I2C clocks before the timeout is asserted. |

This function enables and configures the clock low timeout feature in the I2C peripheral. This feature is implemented as a 12-bit counter, with the upper 8-bits being programmable. For example, to program a timeout of 20ms with a 100-kHz SCL frequency, ui32Value is 0x7d.

Definition at line 1442 of file i2c.c.

References ASSERT, HWREG, and I2C_O_MCLKOCNT.

| void I2CRxFIFOConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the I2C receive (RX) FIFO.

| ui32Base | is the base address of the I2C module. |

| ui32Config | is the configuration of the FIFO using specified macros. |

This configures the I2C peripheral's receive FIFO. The receive FIFO can be used by the master or slave, but not both. The following macros are used to configure the RX FIFO behavior for master or slave, with or without DMA:

I2C_FIFO_CFG_RX_MASTER, I2C_FIFO_CFG_RX_SLAVE, I2C_FIFO_CFG_RX_MASTER_DMA, I2C_FIFO_CFG_RX_SLAVE_DMA

To select the trigger level, one of the following macros should be used:

I2C_FIFO_CFG_RX_TRIG_1, I2C_FIFO_CFG_RX_TRIG_2, I2C_FIFO_CFG_RX_TRIG_3, I2C_FIFO_CFG_RX_TRIG_4, I2C_FIFO_CFG_RX_TRIG_5, I2C_FIFO_CFG_RX_TRIG_6, I2C_FIFO_CFG_RX_TRIG_7, I2C_FIFO_CFG_RX_TRIG_8

Definition at line 1729 of file i2c.c.

References ASSERT, HWREG, and I2C_O_FIFOCTL.

| void I2CRxFIFOFlush | ( | uint32_t | ui32Base | ) |

Flushes the receive (RX) FIFO.

| ui32Base | is the base address of the I2C module. |

This function flushes the I2C receive FIFO.

Definition at line 1762 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOCTL_RXFLUSH, and I2C_O_FIFOCTL.

| void I2CSlaveACKOverride | ( | uint32_t | ui32Base, |

| bool | bEnable | ||

| ) |

Configures ACK override behavior of the I2C Slave.

| ui32Base | is the base address of the I2C module. |

| bEnable | enables or disables ACK override. |

This function enables or disables ACK override, allowing the user application to drive the value on SDA during the ACK cycle.

Definition at line 1472 of file i2c.c.

References ASSERT, HWREG, I2C_O_SACKCTL, and I2C_SACKCTL_ACKOEN.

| void I2CSlaveACKValueSet | ( | uint32_t | ui32Base, |

| bool | bACK | ||

| ) |

Writes the ACK value.

| ui32Base | is the base address of the I2C module. |

| bACK | chooses whether to ACK (true) or NACK (false) the transfer. |

This function puts the desired ACK value on SDA during the ACK cycle. The value written is only valid when ACK override is enabled using I2CSlaveACKOverride().

Definition at line 1507 of file i2c.c.

References ASSERT, HWREG, I2C_O_SACKCTL, and I2C_SACKCTL_ACKOVAL.

| void I2CSlaveAddressSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8AddrNum, | ||

| uint8_t | ui8SlaveAddr | ||

| ) |

Sets the I2C slave address.

| ui32Base | is the base address of the I2C module. |

| ui8AddrNum | determines which slave address is set. |

| ui8SlaveAddr | is the 7-bit slave address |

This function writes the specified slave address. The ui32AddrNum field dictates which slave address is configured. For example, a value of 0 configures the primary address and a value of 1 configures the secondary.

Definition at line 307 of file i2c.c.

References ASSERT, HWREG, I2C_O_SOAR, I2C_O_SOAR2, and I2C_SOAR2_OAR2EN.

| uint32_t I2CSlaveDataGet | ( | uint32_t | ui32Base | ) |

Receives a byte that has been sent to the I2C Slave.

| ui32Base | is the base address of the I2C module. |

This function reads a byte of data from the I2C Slave Data Register.

Definition at line 1613 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SDR.

| void I2CSlaveDataPut | ( | uint32_t | ui32Base, |

| uint8_t | ui8Data | ||

| ) |

Transmits a byte from the I2C Slave.

| ui32Base | is the base address of the I2C module. |

| ui8Data | is the data to be transmitted from the I2C Slave |

This function places the supplied data into I2C Slave Data Register.

Definition at line 1587 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SDR.

| void I2CSlaveDisable | ( | uint32_t | ui32Base | ) |

Disables the I2C slave block.

| ui32Base | is the base address of the I2C module. |

This function disables operation of the I2C slave block.

Definition at line 433 of file i2c.c.

References ASSERT, HWREG, I2C_MCR_SFE, I2C_O_MCR, and I2C_O_SCSR.

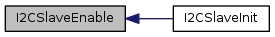

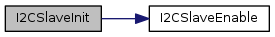

| void I2CSlaveEnable | ( | uint32_t | ui32Base | ) |

Enables the I2C Slave block.

| ui32Base | is the base address of the I2C module. |

This fucntion enables operation of the I2C Slave block.

Definition at line 378 of file i2c.c.

References ASSERT, HWREG, I2C_MCR_SFE, I2C_O_MCR, I2C_O_SCSR, and I2C_SCSR_DA.

Referenced by I2CSlaveInit().

| void I2CSlaveFIFODisable | ( | uint32_t | ui32Base | ) |

Disable FIFO usage for the I2C Slave.

| ui32Base | is the base address of the I2C module. |

This function disables the FIFOs for the I2C Slave. After calling this this function, the FIFOs are disabled, but the Slave remains active.

Definition at line 2125 of file i2c.c.

References ASSERT, HWREG, I2C_O_SCSR, and I2C_SCSR_DA.

| void I2CSlaveFIFOEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Enables FIFO usage for the I2C Slave.

| ui32Base | is the base address of the I2C module. |

| ui32Config | is the desired FIFO configuration of the I2C Slave. |

This function configures the I2C Slave to use the FIFO(s). This function should be used in combination with I2CTxFIFOConfigSet() and/or I2CRxFIFOConfigSet(), which configure the FIFO trigger level and tell the FIFO hardware whether to interact with the I2C Master or Slave. The application appropriate combination of I2C_SLAVE_TX_FIFO_ENABLE and I2C_SLAVE_RX_FIFO_ENABLE should be passed in to the ui32Config field.

The Slave I2CSCSR register is write-only, so any call to I2CSlaveEnable(), I2CSlaveDisable or I2CSlaveFIFOEnable() overwrites the slave configuration. Therefore, application software should call I2CSlaveEnable() followed by I2CSlaveFIFOEnable() with the desired FIFO configuration.

Definition at line 2096 of file i2c.c.

References ASSERT, HWREG, I2C_O_SCSR, and I2C_SCSR_DA.

| void I2CSlaveInit | ( | uint32_t | ui32Base, |

| uint8_t | ui8SlaveAddr | ||

| ) |

Initializes the I2C Slave block.

| ui32Base | is the base address of the I2C module. |

| ui8SlaveAddr | 7-bit slave address |

This function initializes operation of the I2C Slave block by configuring the slave address and enabling the I2C Slave block.

The parameter ui8SlaveAddr is the value that is compared against the slave address sent by an I2C master.

Definition at line 269 of file i2c.c.

References ASSERT, HWREG, I2C_O_SOAR, and I2CSlaveEnable().

| void I2CSlaveIntClear | ( | uint32_t | ui32Base | ) |

Clears I2C Slave interrupt sources.

| ui32Base | is the base address of the I2C module. |

The I2C Slave interrupt source is cleared, so that it no longer asserts. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

Definition at line 1057 of file i2c.c.

References ASSERT, HWREG, I2C_O_SICR, and I2C_SICR_DATAIC.

| void I2CSlaveIntClearEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears I2C Slave interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. |

The specified I2C Slave interrupt sources are cleared, so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

The ui32IntFlags parameter has the same definition as the ui32IntFlags parameter to I2CSlaveIntEnableEx().

Definition at line 1097 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SICR.

| void I2CSlaveIntDisable | ( | uint32_t | ui32Base | ) |

Disables the I2C Slave interrupt.

| ui32Base | is the base address of the I2C module. |

This function disables the I2C Slave interrupt source.

Definition at line 754 of file i2c.c.

References ASSERT, HWREG, I2C_O_SIMR, and I2C_SLAVE_INT_DATA.

| void I2CSlaveIntDisableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables individual I2C Slave interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. |

This function disables the indicated I2C Slave interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter has the same definition as the ui32IntFlags parameter to I2CSlaveIntEnableEx().

Definition at line 786 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SIMR.

| void I2CSlaveIntEnable | ( | uint32_t | ui32Base | ) |

Enables the I2C Slave interrupt.

| ui32Base | is the base address of the I2C module. |

This function enables the I2C Slave interrupt source.

Definition at line 628 of file i2c.c.

References ASSERT, HWREG, I2C_O_SIMR, and I2C_SLAVE_INT_DATA.

| void I2CSlaveIntEnableEx | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables individual I2C Slave interrupt sources.

| ui32Base | is the base address of the I2C module. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. |

This function enables the indicated I2C Slave interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 672 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SIMR.

| bool I2CSlaveIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current I2C Slave interrupt status.

| ui32Base | is the base address of the I2C module. |

| bMasked | is false if the raw interrupt status is requested and true if the masked interrupt status is requested. |

This function returns the interrupt status for the I2C Slave. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 892 of file i2c.c.

References ASSERT, HWREG, I2C_O_SMIS, and I2C_O_SRIS.

| uint32_t I2CSlaveIntStatusEx | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current I2C Slave interrupt status.

| ui32Base | is the base address of the I2C module. |

| bMasked | is false if the raw interrupt status is requested and true if the masked interrupt status is requested. |

This function returns the interrupt status for the I2C Slave. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 930 of file i2c.c.

References ASSERT, HWREG, I2C_O_SMIS, and I2C_O_SRIS.

| uint32_t I2CSlaveStatus | ( | uint32_t | ui32Base | ) |

Gets the I2C Slave status

| ui32Base | is the base address of the I2C module. |

This function returns the action requested from a master, if any. Possible values are:

Definition at line 1561 of file i2c.c.

References ASSERT, HWREG, and I2C_O_SCSR.

| void I2CTxFIFOConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the I2C transmit (TX) FIFO.

| ui32Base | is the base address of the I2C module. |

| ui32Config | is the configuration of the FIFO using specified macros. |

This configures the I2C peripheral's transmit FIFO. The transmit FIFO can be used by the master or slave, but not both. The following macros are used to configure the TX FIFO behavior for master or slave, with or without DMA:

I2C_FIFO_CFG_TX_MASTER, I2C_FIFO_CFG_TX_SLAVE, I2C_FIFO_CFG_TX_MASTER_DMA, I2C_FIFO_CFG_TX_SLAVE_DMA

To select the trigger level, one of the following macros should be used:

I2C_FIFO_CFG_TX_TRIG_1, I2C_FIFO_CFG_TX_TRIG_2, I2C_FIFO_CFG_TX_TRIG_3, I2C_FIFO_CFG_TX_TRIG_4, I2C_FIFO_CFG_TX_TRIG_5, I2C_FIFO_CFG_TX_TRIG_6, I2C_FIFO_CFG_TX_TRIG_7, I2C_FIFO_CFG_TX_TRIG_8

Definition at line 1655 of file i2c.c.

References ASSERT, HWREG, and I2C_O_FIFOCTL.

| void I2CTxFIFOFlush | ( | uint32_t | ui32Base | ) |

Flushes the transmit (TX) FIFO.

| ui32Base | is the base address of the I2C module. |

This function flushes the I2C transmit FIFO.

Definition at line 1688 of file i2c.c.

References ASSERT, HWREG, I2C_FIFOCTL_TXFLUSH, and I2C_O_FIFOCTL.

|

static |

|

static |

|

static |

Definition at line 63 of file i2c.c.

Referenced by _I2CIntNumberGet().

|

static |

Definition at line 76 of file i2c.c.

Referenced by _I2CIntNumberGet().