|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Data Structures | |

| union | tEMACDES3 |

| struct | tEMACDMADescriptor |

| A structure defining a single Ethernet DMA buffer descriptor. More... | |

| struct | tEMACWakeUpFrameFilter |

Typedefs | |

| typedef struct tEMACDMADescriptor | tEMACDMADescriptor |

Functions | |

| void | EMACInit (uint32_t ui32Base, uint32_t ui32SysClk, uint32_t ui32BusConfig, uint32_t ui32RxBurst, uint32_t ui32TxBurst, uint32_t ui32DescSkipSize) |

| void | EMACReset (uint32_t ui32Base) |

| void | EMACPHYConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | EMACConfigSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32ModeFlags, uint32_t ui32RxMaxFrameSize) |

| void | EMACConfigGet (uint32_t ui32Base, uint32_t *pui32Config, uint32_t *pui32Mode, uint32_t *pui32RxMaxFrameSize) |

| void | EMACAddrSet (uint32_t ui32Base, uint32_t ui32Index, const uint8_t *pui8MACAddr) |

| void | EMACAddrGet (uint32_t ui32Base, uint32_t ui32Index, uint8_t *pui8MACAddr) |

| uint32_t | EMACNumAddrGet (uint32_t ui32Base) |

| void | EMACAddrFilterSet (uint32_t ui32Base, uint32_t ui32Index, uint32_t ui32Config) |

| uint32_t | EMACAddrFilterGet (uint32_t ui32Base, uint32_t ui32Index) |

| void | EMACFrameFilterSet (uint32_t ui32Base, uint32_t ui32FilterOpts) |

| uint32_t | EMACFrameFilterGet (uint32_t ui32Base) |

| void | EMACHashFilterSet (uint32_t ui32Base, uint32_t ui32HashHi, uint32_t ui32HashLo) |

| void | EMACHashFilterGet (uint32_t ui32Base, uint32_t *pui32HashHi, uint32_t *pui32HashLo) |

| uint32_t | EMACHashFilterBitCalculate (uint8_t *pui8MACAddr) |

| void | EMACRxWatchdogTimerSet (uint32_t ui32Base, uint8_t ui8Timeout) |

| uint32_t | EMACStatusGet (uint32_t ui32Base) |

| void | EMACTxDMAPollDemand (uint32_t ui32Base) |

| void | EMACRxDMAPollDemand (uint32_t ui32Base) |

| void | EMACRxDMADescriptorListSet (uint32_t ui32Base, tEMACDMADescriptor *pDescriptor) |

| tEMACDMADescriptor * | EMACRxDMADescriptorListGet (uint32_t ui32Base) |

| tEMACDMADescriptor * | EMACRxDMACurrentDescriptorGet (uint32_t ui32Base) |

| uint8_t * | EMACRxDMACurrentBufferGet (uint32_t ui32Base) |

| void | EMACTxDMADescriptorListSet (uint32_t ui32Base, tEMACDMADescriptor *pDescriptor) |

| tEMACDMADescriptor * | EMACTxDMADescriptorListGet (uint32_t ui32Base) |

| tEMACDMADescriptor * | EMACTxDMACurrentDescriptorGet (uint32_t ui32Base) |

| uint8_t * | EMACTxDMACurrentBufferGet (uint32_t ui32Base) |

| uint32_t | EMACDMAStateGet (uint32_t ui32Base) |

| void | EMACTxFlush (uint32_t ui32Base) |

| void | EMACTxEnable (uint32_t ui32Base) |

| void | EMACTxDisable (uint32_t ui32Base) |

| void | EMACRxEnable (uint32_t ui32Base) |

| void | EMACRxDisable (uint32_t ui32Base) |

| void | EMACIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | EMACIntUnregister (uint32_t ui32Base) |

| void | EMACIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | EMACIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| uint32_t | EMACIntStatus (uint32_t ui32Base, bool bMasked) |

| void | EMACIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | EMACPHYWrite (uint32_t ui32Base, uint8_t ui8PhyAddr, uint8_t ui8RegAddr, uint16_t ui16Data) |

| uint16_t | EMACPHYRead (uint32_t ui32Base, uint8_t ui8PhyAddr, uint8_t ui8RegAddr) |

| uint16_t | EMACPHYExtendedRead (uint32_t ui32Base, uint8_t ui8PhyAddr, uint16_t ui16RegAddr) |

| void | EMACPHYExtendedWrite (uint32_t ui32Base, uint8_t ui8PhyAddr, uint16_t ui16RegAddr, uint16_t ui16Value) |

| void | EMACPHYPowerOff (uint32_t ui32Base, uint8_t ui8PhyAddr) |

| void | EMACPHYPowerOn (uint32_t ui32Base, uint8_t ui8PhyAddr) |

| void | EMACTimestampConfigSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32SubSecondInc) |

| uint32_t | EMACTimestampConfigGet (uint32_t ui32Base, uint32_t *pui32SubSecondInc) |

| void | EMACTimestampEnable (uint32_t ui32Base) |

| void | EMACTimestampDisable (uint32_t ui32Base) |

| void | EMACTimestampSysTimeSet (uint32_t ui32Base, uint32_t ui32Seconds, uint32_t ui32SubSeconds) |

| void | EMACTimestampSysTimeGet (uint32_t ui32Base, uint32_t *pui32Seconds, uint32_t *pui32SubSeconds) |

| void | EMACTimestampSysTimeUpdate (uint32_t ui32Base, uint32_t ui32Seconds, uint32_t ui32SubSeconds, bool bInc) |

| void | EMACTimestampAddendSet (uint32_t ui32Base, uint32_t ui32Increment) |

| void | EMACTimestampTargetSet (uint32_t ui32Base, uint32_t ui32Seconds, uint32_t ui32SubSeconds) |

| void | EMACTimestampTargetIntEnable (uint32_t ui32Base) |

| void | EMACTimestampTargetIntDisable (uint32_t ui32Base) |

| uint32_t | EMACTimestampIntStatus (uint32_t ui32Base) |

| void | EMACTimestampPPSSimpleModeSet (uint32_t ui32Base, uint32_t ui32FreqConfig) |

| void | EMACTimestampPPSCommandModeSet (uint32_t ui32Base, uint32_t ui32Config) |

| Configures the Ethernet MAC PPS output in command mode. More... | |

| void | EMACTimestampPPSCommand (uint32_t ui32Base, uint8_t ui8Cmd) |

| void | EMACTimestampPPSPeriodSet (uint32_t ui32Base, uint32_t ui32Period, uint32_t ui32Width) |

| void | EMACVLANRxConfigSet (uint32_t ui32Base, uint16_t ui16Tag, uint32_t ui32Config) |

| uint32_t | EMACVLANRxConfigGet (uint32_t ui32Base, uint16_t *pui16Tag) |

| void | EMACVLANTxConfigSet (uint32_t ui32Base, uint16_t ui16Tag, uint32_t ui32Config) |

| uint32_t | EMACVLANTxConfigGet (uint32_t ui32Base, uint16_t *pui16Tag) |

| uint32_t | EMACVLANHashFilterBitCalculate (uint16_t ui16Tag) |

| void | EMACVLANHashFilterSet (uint32_t ui32Base, uint32_t ui32Hash) |

| uint32_t | EMACVLANHashFilterGet (uint32_t ui32Base) |

| void | EMACRemoteWakeUpFrameFilterSet (uint32_t ui32Base, const tEMACWakeUpFrameFilter *pFilter) |

| void | EMACRemoteWakeUpFrameFilterGet (uint32_t ui32Base, tEMACWakeUpFrameFilter *pFilter) |

| void | EMACPowerManagementControlSet (uint32_t ui32Base, uint32_t ui32Flags) |

| uint32_t | EMACPowerManagementControlGet (uint32_t ui32Base) |

| uint32_t | EMACPowerManagementStatusGet (uint32_t ui32Base) |

Variables | |

| struct { | |

| uint32_t ui32SysClockMax | |

| uint32_t ui32Divisor | |

| } | g_pi16MIIClockDiv [] |

| #define EMAC_ABNORMAL_INTS |

Definition at line 148 of file emac.c.

Referenced by EMACIntClear(), EMACIntDisable(), and EMACIntEnable().

| #define EMAC_CONFIG_RX_ENABLED 0x00000004 |

Definition at line 496 of file emac.h.

Referenced by EMACConfigGet(), and EMACConfigSet().

| #define EMAC_CONFIG_TX_ENABLED 0x00000008 |

Definition at line 495 of file emac.h.

Referenced by EMACConfigGet(), and EMACConfigSet().

| #define EMAC_FILTER_ADDR_ENABLE 0x80000000 |

Definition at line 605 of file emac.h.

Referenced by EMACAddrFilterGet(), and EMACAddrFilterSet().

| #define EMAC_FILTER_BYTE_MASK_M 0x3F000000 |

Definition at line 614 of file emac.h.

Referenced by EMACAddrFilterGet(), and EMACAddrFilterSet().

| #define EMAC_FILTER_SOURCE_ADDR 0x40000000 |

Definition at line 606 of file emac.h.

Referenced by EMACAddrFilterGet(), and EMACAddrFilterSet().

| #define EMAC_INT_ABNORMAL_INT 0x00008000 |

Definition at line 709 of file emac.h.

Referenced by EMACIntClear(), EMACIntDisable(), and EMACIntEnable().

| #define EMAC_INT_NORMAL_INT 0x00010000 |

Definition at line 708 of file emac.h.

Referenced by EMACIntClear(), EMACIntDisable(), and EMACIntEnable().

| #define EMAC_INT_PHY 0x80000000 |

Definition at line 677 of file emac.h.

Referenced by EMACIntClear(), EMACIntDisable(), EMACIntEnable(), and EMACIntStatus().

| #define EMAC_MASKABLE_INTS |

| #define EMAC_NON_MASKED_INTS |

| #define EMAC_NORMAL_INTS |

Definition at line 138 of file emac.c.

Referenced by EMACIntClear(), EMACIntDisable(), and EMACIntEnable().

| #define EMAC_O_ADDRH | ( | n | ) | (EMAC_O_ADDR0H + (MAC_ADDR_OFFSET * (n))) |

Definition at line 182 of file emac.c.

Referenced by EMACAddrFilterGet(), EMACAddrFilterSet(), EMACAddrGet(), and EMACAddrSet().

| #define EMAC_O_ADDRL | ( | n | ) | (EMAC_O_ADDR0L + (MAC_ADDR_OFFSET * (n))) |

Definition at line 181 of file emac.c.

Referenced by EMACAddrFilterSet(), EMACAddrGet(), and EMACAddrSet().

| #define EMAC_PHY_TYPE_EXTERNAL_RMII 0xC0000000 |

Definition at line 385 of file emac.h.

Referenced by EMACPHYConfigSet().

| #define EMAC_PHY_TYPE_INTERNAL 0x00000000 |

Definition at line 383 of file emac.h.

Referenced by EMACPHYConfigSet().

| #define EMAC_PHY_TYPE_MASK 0xC0000000 |

Definition at line 416 of file emac.h.

Referenced by EMACPHYConfigSet().

| #define EMAC_PMT_GLOBAL_UNICAST_ENABLE 0x00000200 |

Definition at line 885 of file emac.h.

Referenced by EMACPowerManagementControlSet().

| #define EMAC_PMT_MAGIC_PACKET_ENABLE 0x00000002 |

Definition at line 887 of file emac.h.

Referenced by EMACPowerManagementControlSet().

| #define EMAC_PMT_POWER_DOWN 0x00000001 |

Definition at line 888 of file emac.h.

Referenced by EMACPowerManagementControlSet().

| #define EMAC_PMT_WAKEUP_PACKET_ENABLE 0x00000004 |

Definition at line 886 of file emac.h.

Referenced by EMACPowerManagementControlSet().

| #define EMAC_PPS_1HZ 0x00000001 |

Definition at line 736 of file emac.h.

Referenced by EMACTimestampPPSSimpleModeSet().

| #define EMAC_PPS_32768HZ 0x00000010 |

Definition at line 751 of file emac.h.

Referenced by EMACTimestampPPSSimpleModeSet().

| #define EMAC_PPS_SINGLE_PULSE 0x00000000 |

Definition at line 735 of file emac.h.

Referenced by EMACTimestampPPSSimpleModeSet().

| #define EMAC_PPS_TARGET_BOTH 0x00000040 |

Definition at line 761 of file emac.h.

Referenced by EMACTimestampPPSCommandModeSet().

| #define EMAC_PPS_TARGET_INT 0x00000000 |

Definition at line 759 of file emac.h.

Referenced by EMACTimestampPPSCommandModeSet().

| #define EMAC_PPS_TARGET_PPS 0x00000060 |

Definition at line 760 of file emac.h.

Referenced by EMACTimestampPPSCommandModeSet().

| #define EMAC_RX_DMA_STATE | ( | x | ) | ((x) & EMAC_DMA_RXSTAT_MASK) |

| #define EMAC_TS_DIGITAL_ROLLOVER 0x00000200 |

Definition at line 638 of file emac.h.

Referenced by EMACTimestampPPSSimpleModeSet().

| #define EMAC_TX_DMA_STATE | ( | x | ) | ((x) & EMAC_DMA_TXSTAT_MASK) |

| #define htonl | ( | a | ) |

| #define htons | ( | a | ) |

| #define MAC_ADDR_OFFSET (EMAC_O_ADDR1L - EMAC_O_ADDR0L) |

| #define NUM_CLOCK_DIVISORS |

Definition at line 207 of file emac.c.

Referenced by EMACInit().

| #define NUM_MAC_ADDR 4 |

Definition at line 173 of file emac.c.

Referenced by EMACAddrFilterGet(), EMACAddrFilterSet(), EMACAddrGet(), EMACAddrSet(), and EMACNumAddrGet().

| #define VALID_CONFIG_FLAGS |

| #define VALID_FRMFILTER_FLAGS |

Definition at line 96 of file emac.c.

Referenced by EMACFrameFilterGet(), and EMACFrameFilterSet().

| typedef struct tEMACDMADescriptor tEMACDMADescriptor |

| uint32_t EMACAddrFilterGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Index | ||

| ) |

Gets filtering parameters associated with one of the configured MAC addresses.

| ui32Base | is the base address of the controller. |

| ui32Index | is the index of the MAC address slot for which the filter is to be queried. |

This function returns filtering parameters associated with one of the MAC address slots that the controller supports. This configuration is used when perfect filtering (rather than hash table filtering) is selected.

Valid values for ui32Index are from 1 to (number of MAC address slots - 1). The number of supported MAC address slots may be found by calling EMACNumAddrGet(). MAC index 0 is the local MAC address and does not have filtering parameters associated with it.

Definition at line 1394 of file emac.c.

References ASSERT, EMAC_FILTER_ADDR_ENABLE, EMAC_FILTER_BYTE_MASK_M, EMAC_FILTER_SOURCE_ADDR, EMAC_O_ADDRH, HWREG, and NUM_MAC_ADDR.

| void EMACAddrFilterSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Index, | ||

| uint32_t | ui32Config | ||

| ) |

Sets filtering parameters associated with one of the configured MAC addresses.

| ui32Base | is the base address of the controller. |

| ui32Index | is the index of the MAC address slot for which the filter is to be set. |

| ui32Config | sets the filter parameters for the given MAC address. |

This function sets filtering parameters associated with one of the MAC address slots that the controller supports. This configuration is used when perfect filtering (rather than hash table filtering) is selected.

Valid values for ui32Index are from 1 to (number of MAC address slots - 1). The number of supported MAC address slots may be found by calling EMACNumAddrGet(). MAC index 0 is the local MAC address and does not have filtering parameters associated with it.

The ui32Config parameter determines how the given MAC address is used when filtering incoming Ethernet frames. It is comprised of a logical OR of the fields:

Definition at line 1323 of file emac.c.

References ASSERT, EMAC_FILTER_ADDR_ENABLE, EMAC_FILTER_BYTE_MASK_M, EMAC_FILTER_SOURCE_ADDR, EMAC_O_ADDRH, EMAC_O_ADDRL, HWREG, and NUM_MAC_ADDR.

| void EMACAddrGet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Index, | ||

| uint8_t * | pui8MACAddr | ||

| ) |

Gets one of the MAC addresses stored in the Ethernet controller.

| ui32Base | is the base address of the controller. |

| ui32Index | is the zero-based index of the MAC address to return. |

| pui8MACAddr | is the pointer to the location in which to store the array of MAC-48 address octets. |

This function reads the currently programmed MAC address into the pui8MACAddr buffer. The ui32Index parameter defines which of the hardware's MAC addresses to return. The number of MAC addresses supported by the controller may be queried using a call to EMACNumAddrGet(). Index 0 refers to the MAC address of the local node. Other indices are used to define MAC addresses when filtering incoming packets.

The address is written to the pui8MACAddr array ordered with the first byte to be transmitted in the first array entry. For example, if the address is written in its usual form with the Organizationally Unique Identifier (OUI) shown first as:

AC-DE-48-00-00-80

the data is returned with 0xAC in the first byte of the array, 0xDE in the second, 0x48 in the third and so on.

Definition at line 1226 of file emac.c.

References ASSERT, EMAC_O_ADDRH, EMAC_O_ADDRL, HWREG, and NUM_MAC_ADDR.

| void EMACAddrSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Index, | ||

| const uint8_t * | pui8MACAddr | ||

| ) |

Sets the MAC address of the Ethernet controller.

| ui32Base | is the base address of the Ethernet controller. |

| ui32Index | is the zero-based index of the MAC address to set. |

| pui8MACAddr | is the pointer to the array of MAC-48 address octets. |

This function programs the IEEE-defined MAC-48 address specified in pui8MACAddr into the Ethernet controller. This address is used by the Ethernet controller for hardware-level filtering of incoming Ethernet packets (when promiscuous mode is not enabled). Index 0 is used to hold the local node's MAC address which is inserted into all transmitted packets.

The controller may support several Ethernet MAC address slots, each of which may be programmed independently and used to filter incoming packets. The number of MAC addresses that the hardware supports may be queried using a call to EMACNumAddrGet(). The value of the ui32Index parameter must lie in the range from 0 to (number of MAC addresses - 1) inclusive.

The MAC-48 address is defined as 6 octets, illustrated by the following example address. The numbers are shown in hexadecimal format.

AC-DE-48-00-00-80

In this representation, the first three octets (AC-DE-48) are the Organizationally Unique Identifier (OUI). This is a number assigned by the IEEE to an organization that requests a block of MAC addresses. The last three octets (00-00-80) are a 24-bit number managed by the OUI owner to uniquely identify a piece of hardware within that organization that is to be connected to the Ethernet.

In this representation, the octets are transmitted from left to right, with the AC'' octet being transmitted first and the80'' octet being transmitted last. Within an octet, the bits are transmitted LSB to MSB. For this address, the first bit to be transmitted would be 0'', the LSB ofAC'', and the last bit to be transmitted would be 1'', the MSB of 80''.

The address passed to this function in the pui8MACAddr array is ordered with the first byte to be transmitted in the first array entry. For example, the address given above could be represented using the following array:

uint8_t g_pui8MACAddr[] = { 0xAC, 0xDE, 0x48, 0x00, 0x00, 0x80 };

If the MAC address set by this function is currently enabled, it remains enabled following this call. Similarly, any filter configured for the MAC address remains unaffected by a change in the address.

Definition at line 1171 of file emac.c.

References ASSERT, EMAC_O_ADDRH, EMAC_O_ADDRL, HWREG, and NUM_MAC_ADDR.

| void EMACConfigGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Config, | ||

| uint32_t * | pui32Mode, | ||

| uint32_t * | pui32RxMaxFrameSize | ||

| ) |

Returns the Ethernet MAC's current basic configuration parameters.

| ui32Base | is the base address of the Ethernet controller. |

| pui32Config | points to storage that is written with Ethernet MAC configuration. |

| pui32Mode | points to storage that is written with Ethernet MAC mode information. |

| pui32RxMaxFrameSize | points to storage that is written with the maximum receive frame size. |

This function is called to query the basic operating parameters for the MAC and its DMA engines.

The pui32Config parameter is written with the logical OR of various fields and flags. The first field describes which MAC address is used during insertion or replacement for all transmitted frames. Valid options are

The interframe gap between transmitted frames is given using one of the following values:

The number of bytes of preamble added to the beginning of every transmitted frame is described using one of the following values:

The back-off limit determines the range of the random time that the MAC delays after a collision and before attempting to retransmit a frame. One of the following values provides the currently selected limit. In each case the retransmission delay in terms of 512 bit time slots, is the lower of (2 ** N) and a random number between 0 and the reported backoff-limit.

Handling of insertion or replacement of the source address in all transmitted frames is described by one of the following fields:

Whether the interface attempts to operate in full- or half-duplex mode is reported by one of the following flags:

The following additional flags may also be included:

The pui32ModeFlags parameter is written with operating parameters related to the internal MAC FIFOs. It comprises a logical OR of the following fields. The first field reports the transmit FIFO threshold. Transmission of a frame begins when this amount of data or a full frame exists in the transmit FIFO. This field should be ignored if EMAC_MODE_TX_STORE_FORWARD is also reported. One of the following values is reported:

The second field reports the receive FIFO threshold. DMA transfers of received data begin either when the receive FIFO contains a full frame or this number of bytes. This field should be ignored if EMAC_MODE_RX_STORE_FORWARD is included. One of the following values is reported:

The following additional flags may be included:

The pui32RxMaxFrameSize is written with the currently configured maximum receive packet size. Packets larger than this are flagged as being in error.

Definition at line 1054 of file emac.c.

References ASSERT, EMAC_CFG_JFEN, EMAC_CONFIG_RX_ENABLED, EMAC_CONFIG_TX_ENABLED, EMAC_O_CFG, EMAC_O_DMAOPMODE, EMAC_O_WDOGTO, EMAC_WDOGTO_PWE, EMAC_WDOGTO_WTO_M, HWREG, and VALID_CONFIG_FLAGS.

| void EMACConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32ModeFlags, | ||

| uint32_t | ui32RxMaxFrameSize | ||

| ) |

Configures basic Ethernet MAC operation parameters.

| ui32Base | is the base address of the Ethernet controller. |

| ui32Config | provides various flags and values configuring the MAC. |

| ui32ModeFlags | provides configuration relating to the transmit and receive DMA engines. |

| ui32RxMaxFrameSize | sets the maximum receive frame size above which an error is reported. |

This function is called to configure basic operating parameters for the MAC and its DMA engines.

The ui32Config parameter is the logical OR of various fields and flags. The first field determines which MAC address is used during insertion or replacement for all transmitted frames. Valid options are

The interframe gap between transmitted frames is controlled using one of the following values:

The number of bytes of preamble added to the beginning of every transmitted frame is selected using one of the following values:

The back-off limit determines the range of the random time that the MAC delays after a collision and before attempting to retransmit a frame. One of the following values must be used to select this limit. In each case, the retransmission delay in terms of 512 bit time slots, is the lower of (2 ** N) and a random number between 0 and the selected backoff-limit.

Control over insertion or replacement of the source address in all transmitted frames is provided by using one of the following fields:

Whether the interface attempts to operate in full- or half-duplex mode is controlled by one of the following flags:

The following additional flags may also be specified:

The ui32ModeFlags parameter sets operating parameters related to the internal MAC FIFOs. It comprises a logical OR of the following fields. The first selects the transmit FIFO threshold. Transmission of a frame begins when this amount of data or a full frame exists in the transmit FIFO. This field is ignored if EMAC_MODE_TX_STORE_FORWARD is included. One of the following must be specified:

The second field controls the receive FIFO threshold. DMA transfers of received data begin either when the receive FIFO contains a full frame or this number of bytes. This field is ignored if EMAC_MODE_RX_STORE_FORWARD is included. One of the following must be specified:

The following additional flags may be specified:

The ui32RxMaxFrameSize parameter may be used to override the default setting for the maximum number of bytes that can be received in a frame before that frame is flagged as being in error. If the parameter is set to 0, the default hardware settings are applied. If non-zero, any frame received which is longer than the ui32RxMaxFrameSize, regardless of whether the MAC is configured for normal or Jumbo frame operation, is flagged as an error.

Definition at line 819 of file emac.c.

References ASSERT, EMAC_CFG_PS, EMAC_CONFIG_RX_ENABLED, EMAC_CONFIG_TX_ENABLED, EMAC_O_CFG, EMAC_O_DMAOPMODE, EMAC_O_WDOGTO, EMAC_WDOGTO_PWE, HWREG, and VALID_CONFIG_FLAGS.

| uint32_t EMACDMAStateGet | ( | uint32_t | ui32Base | ) |

Returns the current states of the Ethernet MAC transmit and receive DMA engines.

| ui32Base | is the base address of the controller. |

This function may be used to query the current states of the transmit and receive DMA engines. The return value contains two fields, one providing the transmit state and the other the receive state. Macros EMAC_TX_DMA_STATE() and EMAC_RX_DMA_STATE() may be used to extract these fields from the returned value. Alternatively, masks EMAC_DMA_TXSTAT_MASK and EMAC_DMA_RXSTAT_MASK may be used directly to mask out the individual states from the returned value.

and one of:

Additionally, a DMA bus error may be signaled using EMAC_DMA_ERROR. If this flag is present, the source of the error is identified using one of the following values which may be extracted from the return value using EMAC_DMA_ERR_MASK:

Definition at line 2173 of file emac.c.

References EMAC_DMARIS_AE_M, EMAC_DMARIS_FBI, EMAC_DMARIS_RS_M, EMAC_DMARIS_TS_M, EMAC_O_DMARIS, and HWREG.

| uint32_t EMACFrameFilterGet | ( | uint32_t | ui32Base | ) |

Returns the current Ethernet frame filtering settings.

| ui32Base | is the base address of the controller. |

This function may be called to retrieve the frame filtering configuration set using a prior call to EMACFrameFilterSet().

Control frame filtering configuration is indicated by one of the following values which may be extracted from the returned value using the mask EMAC_FRMFILTER_PASS_MASK:

Definition at line 1564 of file emac.c.

References EMAC_O_FRAMEFLTR, HWREG, and VALID_FRMFILTER_FLAGS.

| void EMACFrameFilterSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32FilterOpts | ||

| ) |

Sets options related to Ethernet frame filtering.

| ui32Base | is the base address of the controller. |

| ui32FilterOpts | is a logical OR of flags defining the required MAC address filtering options. |

This function allows various filtering options to be defined and allows an application to control which frames are received based on various criteria related to the frame source and destination MAC addresses or VLAN tagging.

The ui32FilterOpts parameter is a logical OR of any of the following flags:

Control frame filtering may be configured by ORing one of the following values into ui32FilterOpts:

Definition at line 1484 of file emac.c.

References ASSERT, EMAC_O_FRAMEFLTR, HWREG, and VALID_FRMFILTER_FLAGS.

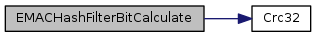

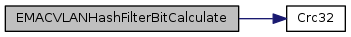

| uint32_t EMACHashFilterBitCalculate | ( | uint8_t * | pui8MACAddr | ) |

Returns the bit number to set in the MAC hash filter corresponding to a given MAC address.

| pui8MACAddr | points to a buffer containing the 6-byte MAC address for which the hash filter bit is to be determined. |

This function may be used to determine which bit in the MAC address hash filter to set to describe a given 6-byte MAC address. The returned value is a 6-bit number where bit 5 indicates which of the two hash table words is affected and the bottom 5 bits indicate the bit number to set within that word. For example, if 0x22 (100010b) is returned, this indicates that bit 2 of word 1 (ui32HashHi as passed to EMACHashFilterSet()) must be set to describe the passed MAC address.

Definition at line 1672 of file emac.c.

References ASSERT, and Crc32().

| void EMACHashFilterGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32HashHi, | ||

| uint32_t * | pui32HashLo | ||

| ) |

Returns the current MAC address hash filter table.

| ui32Base | is the base address of the controller. |

| pui32HashHi | points to storage to be written with the upper 32 bits of the current 64-bit hash filter table. |

| pui32HashLo | points to storage to be written with the lower 32 bits of the current 64-bit hash filter table. |

This function may be used to retrieve the current 64-bit hash filter table from the MAC prior to making changes and setting the new hash filter via a call to EMACHashFilterSet().

Hash table filtering allows many different MAC addresses to be filtered simultaneously at the cost of some false-positive results in the form of packets passing the filter when their MAC address was not one of those required. A CRC of the packet source or destination MAC address is calculated and the bottom 6 bits are used as a bit index into the 64-bit hash filter table. If the bit in the hash table is set, the filter is considered to have passed. If the bit is clear, the filter fails and the packet is rejected (assuming normal rather than inverse filtering is configured).

Definition at line 1638 of file emac.c.

References ASSERT, EMAC_O_HASHTBLH, EMAC_O_HASHTBLL, and HWREG.

| void EMACHashFilterSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32HashHi, | ||

| uint32_t | ui32HashLo | ||

| ) |

Sets the MAC address hash filter table.

| ui32Base | is the base address of the controller. |

| ui32HashHi | is the upper 32 bits of the current 64-bit hash filter table to set. |

| ui32HashLo | is the lower 32 bits of the current 64-bit hash filter table to set. |

This function may be used to set the current 64-bit hash filter table used by the MAC to filter incoming packets when hash filtering is enabled. Hash filtering is enabled by passing EMAC_FRMFILTER_HASH_UNICAST and/or EMAC_FRMFILTER_HASH_MULTICAST in the ui32FilterOpts parameter to EMACFrameFilterSet(). The current hash filter may be retrieved by calling EMACHashFilterGet().

Hash table filtering allows many different MAC addresses to be filtered simultaneously at the cost of some false-positive results (in the form of packets passing the filter when their MAC address was not one of those required). A CRC of the packet source or destination MAC address is calculated and the bottom 6 bits are used as a bit index into the 64-bit hash filter table. If the bit in the hash table is set, the filter is considered to have passed. If the bit is clear, the filter fails and the packet is rejected (assuming normal rather than inverse filtering is configured).

Definition at line 1603 of file emac.c.

References EMAC_O_HASHTBLH, EMAC_O_HASHTBLL, and HWREG.

| void EMACInit | ( | uint32_t | ui32Base, |

| uint32_t | ui32SysClk, | ||

| uint32_t | ui32BusConfig, | ||

| uint32_t | ui32RxBurst, | ||

| uint32_t | ui32TxBurst, | ||

| uint32_t | ui32DescSkipSize | ||

| ) |

Initializes the Ethernet MAC and sets bus-related DMA parameters.

| ui32Base | is the base address of the Ethernet controller. |

| ui32SysClk | is the current system clock frequency in Hertz. |

| ui32BusConfig | defines the bus operating mode for the Ethernet MAC DMA controller. |

| ui32RxBurst | is the maximum receive burst size in words. |

| ui32TxBurst | is the maximum transmit burst size in words. |

| ui32DescSkipSize | is the number of 32-bit words to skip between two unchained DMA descriptors. Values in the range 0 to 31 are valid. |

This function sets bus-related parameters for the Ethernet MAC DMA engines. It must be called after EMACPHYConfigSet() and called again after any subsequent call to EMACPHYConfigSet().

The ui32BusConfig parameter is the logical OR of various fields. The first sets the DMA channel priority weight:

The second field sets the receive and transmit priorities used when arbitrating between the Rx and Tx DMA. The priorities are Rx:Tx unless EMAC_BCONFIG_TX_PRIORITY is also specified, in which case they become Tx:Rx. The priority provided here is ignored if EMAC_BCONFIG_PRIORITY_FIXED is specified.

The following additional flags may also be defined:

The ui32RxBurst and ui32TxBurst parameters indicate the maximum number of words that the relevant DMA should transfer in a single transaction. Valid values are 1, 2, 4, 8, 16 and 32. Any other value results in undefined behavior.

The ui32DescSkipSize parameter is used when the descriptor lists are using ring mode (where descriptors are contiguous in memory with the last descriptor marked with the END_OF_RING flag) rather than chained mode (where each descriptor includes a field that points to the next descriptor in the list). In ring mode, the hardware uses the ui32DescSkipSize to skip past any application-defined fields after the end of the hardware- defined descriptor fields. The parameter value indicates the number of 32-bit words to skip after the last field of the hardware-defined descriptor to get to the first field of the next descriptor. When using arrays of either the tEMACDMADescriptor or tEMACAltDMADescriptor types defined for this driver, ui32DescSkipSize must be set to 1 to skip the pvNext pointer added to the end of each of these structures. Applications may modify these structure definitions to include their own application-specific data and modify ui32DescSkipSize appropriately if desired.

Definition at line 305 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_DMABUSMOD_8XPBL, EMAC_DMABUSMOD_ATDS, EMAC_DMABUSMOD_DSL_S, EMAC_DMABUSMOD_PBL_S, EMAC_DMABUSMOD_RPBL_S, EMAC_DMABUSMOD_SWR, EMAC_DMABUSMOD_USP, EMAC_MIIADDR_CR_M, EMAC_O_DMABUSMOD, EMAC_O_MIIADDR, EMAC_O_MMCRXIM, EMAC_O_MMCTXIM, g_pi16MIIClockDiv, HWREG, NUM_CLOCK_DIVISORS, and ui32SysClockMax.

| void EMACIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears individual Ethernet MAC interrupt sources.

| ui32Base | is the base address of the Ethernet MAC. |

| ui32IntFlags | is the bit mask of the interrupt sources to be cleared. |

This function disables the indicated Ethernet MAC interrupt sources.

The ui32IntFlags parameter is the logical OR of any of the following:

Summary interrupt bits EMAC_INT_NORMAL_INT and EMAC_INT_ABNORMAL_INT are cleared automatically by the driver if any of their constituent sources are cleared. Applications do not need to explicitly clear these bits.

Definition at line 2781 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_ABNORMAL_INTS, EMAC_EPHYMISC_INT, EMAC_INT_ABNORMAL_INT, EMAC_INT_NORMAL_INT, EMAC_INT_PHY, EMAC_NORMAL_INTS, EMAC_O_DMARIS, EMAC_O_EPHYMISC, and HWREG.

| void EMACIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables individual Ethernet MAC interrupt sources.

| ui32Base | is the base address of the Ethernet MAC. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. |

This function disables the indicated Ethernet MAC interrupt sources.

The ui32IntFlags parameter is the logical OR of any of the following:

Summary interrupt bits EMAC_INT_NORMAL_INT and EMAC_INT_ABNORMAL_INT are disabled automatically by the driver if none of their constituent sources are enabled. Applications do not need to explicitly disable these bits.

Definition at line 2561 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_ABNORMAL_INTS, EMAC_EPHYIM_INT, EMAC_INT_ABNORMAL_INT, EMAC_INT_NORMAL_INT, EMAC_INT_PHY, EMAC_MASKABLE_INTS, EMAC_NORMAL_INTS, EMAC_O_DMAIM, EMAC_O_EPHYIM, and HWREG.

| void EMACIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables individual Ethernet MAC interrupt sources.

| ui32Base | is the base address of the Ethernet MAC. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. |

This function enables the indicated Ethernet MAC interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Summary interrupt bits EMAC_INT_NORMAL_INT and EMAC_INT_ABNORMAL_INT are enabled automatically by the driver if any of their constituent sources are enabled. Applications do not need to explicitly enable these bits.

Definition at line 2455 of file emac.c.

References ASSERT, EMAC_ABNORMAL_INTS, EMAC_EPHYIM_INT, EMAC_INT_ABNORMAL_INT, EMAC_INT_NORMAL_INT, EMAC_INT_PHY, EMAC_MASKABLE_INTS, EMAC_NORMAL_INTS, EMAC_O_DMAIM, EMAC_O_EPHYIM, and HWREG.

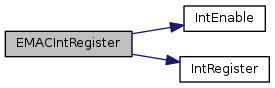

| void EMACIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for an Ethernet interrupt.

| ui32Base | is the base address of the controller. |

| pfnHandler | is a pointer to the function to be called when the enabled Ethernet interrupts occur. |

This function sets the handler to be called when the Ethernet interrupt occurs. This function enables the global interrupt in the interrupt controller; specific Ethernet interrupts must be enabled via EMACIntEnable(). It is the interrupt handler's responsibility to clear the interrupt source.

Definition at line 2346 of file emac.c.

References ASSERT, INT_EMAC0_TM4C129, IntEnable(), and IntRegister().

| uint32_t EMACIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current Ethernet MAC interrupt status.

| ui32Base | is the base address of the Ethernet MAC. |

| bMasked | is true to return the masked interrupt status or false to return the unmasked status. |

This function returns the interrupt status for the Ethernet MAC. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 2676 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_DMARIS_AE_M, EMAC_DMARIS_RS_M, EMAC_DMARIS_TS_M, EMAC_EPHYMISC_INT, EMAC_INT_PHY, EMAC_NON_MASKED_INTS, EMAC_O_DMAIM, EMAC_O_DMARIS, EMAC_O_EPHYMISC, EMAC_O_EPHYRIS, and HWREG.

| void EMACIntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters an interrupt handler for an Ethernet interrupt.

| ui32Base | is the base address of the controller. |

This function unregisters the interrupt handler. This function disables the global interrupt in the interrupt controller so that the interrupt handler is no longer called.

Definition at line 2381 of file emac.c.

References INT_EMAC0_TM4C129, IntDisable(), and IntUnregister().

| uint32_t EMACNumAddrGet | ( | uint32_t | ui32Base | ) |

Returns the number of MAC addresses supported by the Ethernet controller.

| ui32Base | is the base address of the Ethernet controller. |

This function may be used to determine the number of MAC addresses that the given controller supports. MAC address slots may be used when performing perfect (rather than hash table) filtering of packets.

Definition at line 1267 of file emac.c.

References NUM_MAC_ADDR.

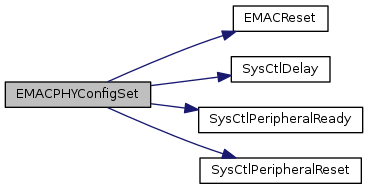

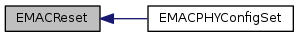

| void EMACPHYConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Selects the Ethernet PHY in use.

| ui32Base | is the base address of the Ethernet controller. |

| ui32Config | selects the PHY in use and, when using the internal PHY, allows various various PHY parameters to be configured. |

This function must be called prior to EMACInit() and EMACConfigSet() to select the Ethernet PHY to be used. If the internal PHY is selected, the function also allows configuration of various PHY parameters. Note that the Ethernet MAC is reset during this function call because parameters used by this function are latched by the hardware only on a MAC reset. The call sequence to select and configure the PHY, therefore, must be as follows:

//! // Enable and reset the MAC.

//! SysCtlPeripheralEnable(SYSCTL_PERIPH_EMAC0);

//! SysCtlPeripheralReset(SYSCTL_PERIPH_EMAC0);

//! if(<using internal PHY>)

//! {

//! // Enable and reset the internal PHY.

//! SysCtlPeripheralEnable(SYSCTL_PERIPH_EPHY0);

//! SysCtlPeripheralReset(SYSCTL_PERIPH_EPHY0);

//! }

//!

//! // Ensure the MAC is completed its reset.

//! while(!MAP_SysCtlPeripheralReady(SYSCTL_PERIPH_EMAC0))

//! {

//! }

//!

//! // Set the PHY type and configuration options.

//! EMACPHYConfigSet(EMAC0_BASE, <config>);

//!

//! // Initialize and configure the MAC.

//! EMACInit(EMAC0_BASE, <system clock rate>, <bus config>,

//! <Rx burst size>, <Tx burst size>, <desc skip>);

//! EMACConfigSet(EMAC0_BASE, <parameters>);

//! The \e ui32Config parameter must specify one of the following values: - \b EMAC_PHY_TYPE_INTERNAL selects the internal Ethernet PHY. - \b EMAC_PHY_TYPE_EXTERNAL_MII selects an external PHY connected via the MII interface. - \b EMAC_PHY_TYPE_EXTERNAL_RMII selects an external PHY connected via the RMII interface. If \b EMAC_PHY_TYPE_INTERNAL is selected, the following flags may be ORed into \e ui32Config to control various PHY features and modes. These flags are ignored if an external PHY is selected. - \b EMAC_PHY_INT_NIB_TXERR_DET_DIS disables odd nibble transmit error detection (sets the default value of PHY register MR10, bit 1). - \b EMAC_PHY_INT_RX_ER_DURING_IDLE enables receive error detection during idle (sets the default value of PHY register MR10, bit 2). - \b EMAC_PHY_INT_ISOLATE_MII_LLOSS ties the MII outputs low if no link is established in 100B-T and full duplex modes (sets the default value of PHY register MR10, bit 3). - \b EMAC_PHY_INT_LINK_LOSS_RECOVERY enables link loss recovery (sets the default value of PHY register MR9, bit 7). - \b EMAC_PHY_INT_TDRRUN enables execution of the TDR procedure after a link down event (sets the default value of PHY register MR9, bit 8). - \b EMAC_PHY_INT_LD_ON_RX_ERR_COUNT enables link down if the receiver error count reaches 32 within a 10-us interval (sets the default value of PHY register MR11 bit 3). - \b EMAC_PHY_INT_LD_ON_MTL3_ERR_COUNT enables link down if the MTL3 error count reaches 20 in a 10 us-interval (sets the default value of PHY register MR11 bit 2). - \b EMAC_PHY_INT_LD_ON_LOW_SNR enables link down if the low SNR threshold is crossed 20 times in a 10 us-interval (sets the default value of PHY register MR11 bit 1). - \b EMAC_PHY_INT_LD_ON_SIGNAL_ENERGY enables link down if energy detector indicates Energy Loss (sets the default value of PHY register MR11 bit 0). - \b EMAC_PHY_INT_POLARITY_SWAP inverts the polarity on both TPTD and TPRD pairs (sets the default value of PHY register MR11 bit 5). - \b EMAC_PHY_INT_MDI_SWAP swaps the MDI pairs putting receive on the TPTD pair and transmit on TPRD (sets the default value of PHY register MR11 bit 6). - \b EMAC_PHY_INT_ROBUST_MDIX enables robust auto MDI-X resolution (sets the default value of PHY register MR9 bit 5). - \b EMAC_PHY_INT_FAST_MDIX enables fast auto-MDI/MDIX resolution (sets the default value of PHY register MR9 bit 6). - \b EMAC_PHY_INT_MDIX_EN enables auto-MDI/MDIX crossover (sets the default value of PHY register MR9 bit 14). - \b EMAC_PHY_INT_FAST_RXDV_DETECT enables fast RXDV detection (set the default value of PHY register MR9 bit 1). - \b EMAC_PHY_INT_FAST_L_UP_DETECT enables fast link-up time during parallel detection (sets the default value of PHY register MR10 bit 6) - \b EMAC_PHY_INT_EXT_FULL_DUPLEX forces full-duplex while working with a link partner in forced 100B-TX (sets the default value of PHY register MR10 bit 5). - \b EMAC_PHY_INT_FAST_AN_80_50_35 enables fast auto-negotiation using break link, link fail inhibit and wait timers set to 80, 50 and 35 respectively (sets the default value of PHY register MR9 bits [4:2] to 3b100). - \b EMAC_PHY_INT_FAST_AN_120_75_50 enables fast auto-negotiation using break link, link fail inhibit and wait timers set to 120, 75 and 50 respectively (sets the default value of PHY register MR9 bits [4:2] to 3b101). - \b EMAC_PHY_INT_FAST_AN_140_150_100 enables fast auto-negotiation using break link, link fail inhibit and wait timers set to 140, 150 and 100 respectively (sets the default value of PHY register MR9 bits [4:2] to 3b110). - \b EMAC_PHY_FORCE_10B_T_HALF_DUPLEX disables auto-negotiation and forces operation in 10Base-T, half duplex mode (sets the default value of PHY register MR9 bits [13:11] to 3b000). - \b EMAC_PHY_FORCE_10B_T_FULL_DUPLEX disables auto-negotiation and forces operation in 10Base-T, full duplex mode (sets the default value of PHY register MR9 bits [13:11] to 3b001). - \b EMAC_PHY_FORCE_100B_T_HALF_DUPLEX disables auto-negotiation and forces operation in 100Base-T, half duplex mode (sets the default value of PHY register MR9 bits [13:11] to 3b010). - \b EMAC_PHY_FORCE_100B_T_FULL_DUPLEX disables auto-negotiation and forces operation in 100Base-T, full duplex mode (sets the default value of PHY register MR9 bits [13:11] to 3b011). - \b EMAC_PHY_AN_10B_T_HALF_DUPLEX enables auto-negotiation and advertises 10Base-T, half duplex mode (sets the default value of PHY register MR9 bits [13:11] to 3b100). - \b EMAC_PHY_AN_10B_T_FULL_DUPLEX enables auto-negotiation and advertises 10Base-T half or full duplex modes (sets the default value of PHY register MR9 bits [13:11] to 3b101). - \b EMAC_PHY_AN_100B_T_HALF_DUPLEX enables auto-negotiation and advertises 10Base-T half or full duplex, and 100Base-T half duplex modes (sets the default value of PHY register MR9 bits [13:11] to 3b110). - \b EMAC_PHY_AN_100B_T_FULL_DUPLEX enables auto-negotiation and advertises 10Base-T half or full duplex, and 100Base-T half or full duplex modes (sets the default value of PHY register MR9 bits [13:11] to 3b111). - \b EMAC_PHY_INT_HOLD prevents the PHY from transmitting energy on the line. As a side effect of this function, the Ethernet MAC is reset so any previous MAC configuration is lost. \return None.

Definition at line 578 of file emac.c.

References EMAC0_BASE, EMAC_CC_CLKEN, EMAC_O_CC, EMAC_O_PC, EMAC_PHY_TYPE_EXTERNAL_RMII, EMAC_PHY_TYPE_INTERNAL, EMAC_PHY_TYPE_MASK, EMACReset(), HWREG, SYSCTL_PERIPH_EPHY0, SysCtlDelay(), SysCtlPeripheralReady(), and SysCtlPeripheralReset().

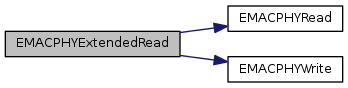

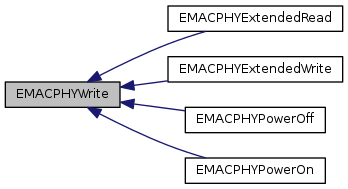

| uint16_t EMACPHYExtendedRead | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr, | ||

| uint16_t | ui16RegAddr | ||

| ) |

Reads from an extended PHY register.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to access. |

| ui16RegAddr | is the address of the PHY extended register to be accessed. |

When using the internal PHY or when connected to an external PHY supporting extended registers, this function returns the contents of the extended PHY register specified by ui16RegAddr.

Definition at line 2953 of file emac.c.

References ASSERT, EMAC0_BASE, EMACPHYRead(), EMACPHYWrite(), EPHY_ADDAR, and EPHY_REGCTL.

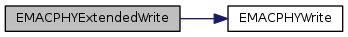

| void EMACPHYExtendedWrite | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr, | ||

| uint16_t | ui16RegAddr, | ||

| uint16_t | ui16Value | ||

| ) |

Writes a value to an extended PHY register.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to access. |

| ui16RegAddr | is the address of the PHY extended register to be accessed. |

| ui16Value | is the value to write to the register. |

When using the internal PHY or when connected to an external PHY supporting extended registers, this function allows a value to be written to the extended PHY register specified by ui16RegAddr.

Definition at line 2993 of file emac.c.

References ASSERT, EMAC0_BASE, EMACPHYWrite(), EPHY_ADDAR, and EPHY_REGCTL.

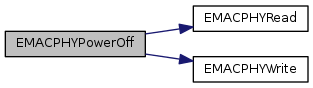

| void EMACPHYPowerOff | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr | ||

| ) |

Powers off the Ethernet PHY.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to power down. |

This function powers off the Ethernet PHY, reducing the current consumption of the device. While in the powered-off state, the Ethernet controller is unable to connect to Ethernet.

Definition at line 3030 of file emac.c.

References EMACPHYRead(), EMACPHYWrite(), EPHY_BMCR, EPHY_BMCR_ANEN, and EPHY_BMCR_PWRDWN.

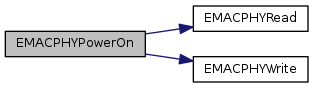

| void EMACPHYPowerOn | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr | ||

| ) |

Powers on the Ethernet PHY.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to power up. |

This function powers on the Ethernet PHY, enabling it return to normal operation. By default, the PHY is powered on, so this function is only called if EMACPHYPowerOff() has previously been called.

Definition at line 3056 of file emac.c.

References EMACPHYRead(), EMACPHYWrite(), EPHY_BMCR, EPHY_BMCR_ANEN, and EPHY_BMCR_PWRDWN.

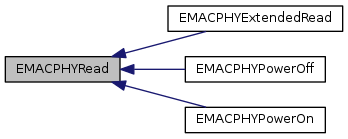

| uint16_t EMACPHYRead | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr, | ||

| uint8_t | ui8RegAddr | ||

| ) |

Reads from a PHY register.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to access. |

| ui8RegAddr | is the address of the PHY register to be accessed. |

This function returns the contents of the PHY register specified by ui8RegAddr.

Definition at line 2900 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_MIIADDR_CR_M, EMAC_MIIADDR_MII_S, EMAC_MIIADDR_MIIB, EMAC_MIIADDR_PLA_S, EMAC_MIIDATA_DATA_M, EMAC_O_MIIADDR, EMAC_O_MIIDATA, and HWREG.

Referenced by EMACPHYExtendedRead(), EMACPHYPowerOff(), and EMACPHYPowerOn().

| void EMACPHYWrite | ( | uint32_t | ui32Base, |

| uint8_t | ui8PhyAddr, | ||

| uint8_t | ui8RegAddr, | ||

| uint16_t | ui16Data | ||

| ) |

Writes to the PHY register.

| ui32Base | is the base address of the controller. |

| ui8PhyAddr | is the physical address of the PHY to access. |

| ui8RegAddr | is the address of the PHY register to be accessed. |

| ui16Data | is the data to be written to the PHY register. |

This function writes the ui16Data value to the PHY register specified by ui8RegAddr.

Definition at line 2843 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_MIIADDR_CR_M, EMAC_MIIADDR_MII_S, EMAC_MIIADDR_MIIB, EMAC_MIIADDR_MIIW, EMAC_MIIADDR_PLA_S, EMAC_O_MIIADDR, EMAC_O_MIIDATA, and HWREG.

Referenced by EMACPHYExtendedRead(), EMACPHYExtendedWrite(), EMACPHYPowerOff(), and EMACPHYPowerOn().

| uint32_t EMACPowerManagementControlGet | ( | uint32_t | ui32Base | ) |

Queries the current Ethernet MAC remote wake-up configuration.

| ui32Base | is the base address of the controller. |

This function allows the MAC's remote wake-up settings to be queried. These settings determine which types of frame should trigger a remote wake-up event

Definition at line 4628 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PMTCTLSTAT, EMAC_PMTCTLSTAT_GLBLUCAST, EMAC_PMTCTLSTAT_MGKPKTEN, EMAC_PMTCTLSTAT_PWRDWN, EMAC_PMTCTLSTAT_WUPFREN, and HWREG.

| void EMACPowerManagementControlSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Flags | ||

| ) |

Sets the Ethernet MAC remote wake-up configuration.

| ui32Base | is the base address of the controller. |

| ui32Flags | defines which types of frame should trigger a remote wake-up and allows the MAC to be put into power-down mode. |

This function allows the MAC's remote wake-up features to be configured, determining which types of frame should trigger a wake-up event and allowing an application to place the MAC in power-down mode. In this mode, the MAC ignores all received frames until one matching a configured remote wake-up frame is received, at which point the MAC automatically exits power-down mode and continues to receive frames.

The ui32Flags parameter is a logical OR of the following flags:

When the MAC is in power-down mode, software may exit the mode by calling this function with the EMAC_PMT_POWER_DOWN flag absent from ui32Flags. If a configured wake-up frame is received while in power-down mode, the EMAC_INT_POWER_MGMNT interrupt is signaled and may be cleared by reading the status using EMACPowerManagementStatusGet().

Definition at line 4576 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PMTCTLSTAT, EMAC_PMT_GLOBAL_UNICAST_ENABLE, EMAC_PMT_MAGIC_PACKET_ENABLE, EMAC_PMT_POWER_DOWN, EMAC_PMT_WAKEUP_PACKET_ENABLE, EMAC_PMTCTLSTAT_GLBLUCAST, EMAC_PMTCTLSTAT_MGKPKTEN, EMAC_PMTCTLSTAT_PWRDWN, EMAC_PMTCTLSTAT_WUPFREN, and HWREG.

| uint32_t EMACPowerManagementStatusGet | ( | uint32_t | ui32Base | ) |

Queries the current Ethernet MAC remote wake-up status.

| ui32Base | is the base address of the controller. |

This function returns information on the remote wake-up state of the Ethernet MAC. If the MAC has been woken up since the last call, the returned value indicates the type of received frame that caused the MAC to exit power-down state.

Definition at line 4668 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PMTCTLSTAT, EMAC_PMTCTLSTAT_MGKPRX, EMAC_PMTCTLSTAT_PWRDWN, EMAC_PMTCTLSTAT_WUPRX, and HWREG.

| void EMACRemoteWakeUpFrameFilterGet | ( | uint32_t | ui32Base, |

| tEMACWakeUpFrameFilter * | pFilter | ||

| ) |

Returns the current remote wake-up frame filter configuration.

| ui32Base | is the base address of the controller. |

| pFilter | points to the structure that is written with the current remote wake-up frame filter information. |

This function may be used to read the current wake-up frame filter settings. The data returned by the function describes wake-up frames in terms of a CRC calculated on up to 31 payload bytes in the frame. The actual bytes used in the CRC calculation are defined by means of a bit mask where a 1'' indicates that a byte in the frame should contribute to the CRC calculation and a0'' indicates that the byte should be skipped, and an offset from the start of the frame to the payload byte that represents the first byte in the 31-byte CRC-checked sequence.

The pFilter parameter points to storage that is written with a structure containing the information defining the frame filters. This structure contains the following fields, each of which is replicated 4 times, once for each possible wake-up frame:

Note that this filter uses CRC16 rather than CRC32 as used in frame checksums.

Definition at line 4494 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PMTCTLSTAT, EMAC_O_RWUFF, EMAC_PMTCTLSTAT_WUPFRRST, and HWREG.

| void EMACRemoteWakeUpFrameFilterSet | ( | uint32_t | ui32Base, |

| const tEMACWakeUpFrameFilter * | pFilter | ||

| ) |

Sets values defining up to four frames used to trigger a remote wake-up.

| ui32Base | is the base address of the controller. |

| pFilter | points to the structure containing remote wake-up frame filter information. |

This function may be used to define up to four different frames that are considered by the Ethernet MAC to be remote wake-up signals. The data passed to the function describes a wake-up frame in terms of a CRC calculated on up to 31 payload bytes in the frame. The actual bytes used in the CRC calculation are defined by means of a bit mask where a ``1'' indicates that a byte in the frame should contribute to the CRC calculation and a ``0'' indicates that the byte should be skipped, as well as an offset from the start of the frame to the payload byte that represents the first byte in the 31-byte CRC-checked sequence.

The pFilter parameter points to a structure containing the information necessary to set up the filters. This structure contains the following fields, each of which is replicated 4 times, once for each possible wake-up frame:

Note that this filter uses CRC16 rather than CRC32 as used in frame checksums. The required CRC uses a direct algorithm with polynomial 0x8005, initial seed value 0xFFFF, no final XOR and reversed data order. CRCs for use in this function may be determined using the online calculator found at http://www.zorc.breitbandkatze.de/crc.html.

Definition at line 4411 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PMTCTLSTAT, EMAC_O_RWUFF, EMAC_PMTCTLSTAT_WUPFRRST, and HWREG.

| void EMACReset | ( | uint32_t | ui32Base | ) |

Resets the Ethernet MAC.

| ui32Base | is the base address of the Ethernet controller. |

This function performs a reset of the Ethernet MAC by resetting all logic and returning all registers to their default values. The function returns only after the hardware indicates that the reset has completed.

Definition at line 425 of file emac.c.

References EMAC_DMABUSMOD_SWR, EMAC_O_DMABUSMOD, and HWREG.

Referenced by EMACPHYConfigSet().

| void EMACRxDisable | ( | uint32_t | ui32Base | ) |

Disables the Ethernet controller receiver.

| ui32Base | is the base address of the controller. |

When terminating operations on the Ethernet interface, this function should be called. This function disables the receiver.

Definition at line 2312 of file emac.c.

References EMAC_CFG_RE, EMAC_DMAOPMODE_SR, EMAC_O_CFG, EMAC_O_DMAOPMODE, and HWREG.

| uint8_t* EMACRxDMACurrentBufferGet | ( | uint32_t | ui32Base | ) |

Returns the current DMA receive buffer pointer.

| ui32Base | is the base address of the controller. |

This function may be called to determine which buffer the receive DMA engine is currently writing to.

Definition at line 1974 of file emac.c.

References EMAC_O_HOSRXBA, and HWREG.

| tEMACDMADescriptor* EMACRxDMACurrentDescriptorGet | ( | uint32_t | ui32Base | ) |

Returns the current DMA receive descriptor pointer.

| ui32Base | is the base address of the controller. |

This function returns a pointer to the current Ethernet receive descriptor read by the DMA.

Definition at line 1952 of file emac.c.

References EMAC_O_HOSRXDESC, and HWREG.

| tEMACDMADescriptor* EMACRxDMADescriptorListGet | ( | uint32_t | ui32Base | ) |

Returns a pointer to the start of the DMA receive descriptor list.

| ui32Base | is the base address of the controller. |

This function returns a pointer to the head of the Ethernet MAC's receive DMA descriptor list. This value corresponds to the pointer originally set using a call to EMACRxDMADescriptorListSet().

Definition at line 1930 of file emac.c.

References EMAC_O_RXDLADDR, and HWREG.

| void EMACRxDMADescriptorListSet | ( | uint32_t | ui32Base, |

| tEMACDMADescriptor * | pDescriptor | ||

| ) |

Sets the DMA receive descriptor list pointer.

| ui32Base | is the base address of the controller. |

| pDescriptor | points to the first DMA descriptor in the list to be passed to the receive DMA engine. |

This function sets the Ethernet MAC's receive DMA descriptor list pointer. The pDescriptor pointer must point to one or more descriptor structures.

When multiple descriptors are provided, they can be either chained or unchained. Chained descriptors are indicated by setting the DES0_TX_CTRL_CHAINED or DES1_RX_CTRL_CHAINED bit in the relevant word of the transmit or receive descriptor. If this bit is clear, unchained descriptors are assumed.

Chained descriptors use a link pointer in each descriptor to point to the next descriptor in the chain.

Unchained descriptors are assumed to be contiguous in memory with a consistent offset between the start of one descriptor and the next. If unchained descriptors are used, the pvLink field in the descriptor becomes available to store a second buffer pointer, allowing each descriptor to point to two buffers rather than one. In this case, the ui32DescSkipSize parameter to EMACInit() must previously have been set to the number of words between the end of one descriptor and the start of the next. This value must be 0 in cases where a packed array of tEMACDMADescriptor structures is used. If the application wishes to add new state fields to the end of the descriptor structure, the skip size should be set to accommodate the newly sized structure.

Applications are responsible for initializing all descriptor fields appropriately before passing the descriptor list to the hardware.

Definition at line 1902 of file emac.c.

References ASSERT, EMAC_O_RXDLADDR, and HWREG.

| void EMACRxDMAPollDemand | ( | uint32_t | ui32Base | ) |

Orders the MAC DMA controller to attempt to acquire the next receive descriptor.

| ui32Base | is the base address of the Ethernet controller. |

This function must be called to restart the receiver if it has been suspended due to the current receive DMA descriptor being owned by the host. Once the application reads any data from the descriptor and marks it as being owned by the MAC DMA, this function causes the hardware to attempt to acquire the descriptor before writing the next received packet into its buffer(s).

Definition at line 1853 of file emac.c.

References EMAC_O_RXPOLLD, and HWREG.

| void EMACRxEnable | ( | uint32_t | ui32Base | ) |

Enables the Ethernet controller receiver.

| ui32Base | is the base address of the controller. |

When starting operations on the Ethernet interface, this function should be called to enable the receiver after all configuration has been completed.

Definition at line 2286 of file emac.c.

References EMAC_CFG_RE, EMAC_DMAOPMODE_SR, EMAC_O_CFG, EMAC_O_DMAOPMODE, and HWREG.

| void EMACRxWatchdogTimerSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8Timeout | ||

| ) |

Sets the receive interrupt watchdog timer period.

| ui32Base | is the base address of the Ethernet controller. |

| ui8Timeout | is the desired timeout expressed as a number of 256 system clock periods. |

This function configures the receive interrupt watchdog timer. The uiTimeout parameter specifies the number of 256 system clock periods that elapse before the timer expires. In cases where the DMA has transferred a frame using a descriptor that has DES1_RX_CTRL_DISABLE_INT set, the watchdog causes a receive interrupt to be generated when it times out. The watchdog timer is reset whenever a packet is transferred to memory using a DMA descriptor that does not disable the receive interrupt.

To disable the receive interrupt watchdog function, set ui8Timeout to 0.

Definition at line 1733 of file emac.c.

References EMAC_O_RXINTWDT, and HWREG.

| uint32_t EMACStatusGet | ( | uint32_t | ui32Base | ) |

Returns the current Ethernet MAC status.

| ui32Base | is the base address of the Ethernet controller. |

This function returns information on the current status of all the main modules in the MAC transmit and receive data paths.

The transmit frame controller status can be extracted from the returned value by ANDing with EMAC_STATUS_TFC_STATE_MASK and is one of the following:

The transmit FIFO read controller status can be extracted from the returned value by ANDing with EMAC_STATUS_TRC_STATE_MASK and is one of the following:

The current receive FIFO levels can be extracted from the returned value by ANDing with EMAC_STATUS_RX_FIFO_LEVEL_MASK and is one of the following:

The current receive FIFO state can be extracted from the returned value by ANDing with EMAC_STATUS_RX_FIFO_STATE_MASK and is one of the following:

Definition at line 1800 of file emac.c.

References EMAC_O_STATUS, and HWREG.

| void EMACTimestampAddendSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Increment | ||

| ) |

Adjusts the system time update rate when using the fine correction method.

| ui32Base | is the base address of the controller. |

| ui32Increment | is the number to add to the accumulator register on each tick of the 25-MHz main oscillator. |

This function is used to control the rate of update of the system time when in fine update mode. Fine correction mode is selected if EMAC_TS_UPDATE_FINE is supplied in the ui32Config parameter passed to a previous call to EMACTimestampConfigSet(). Fine update mode is typically used when synchronizing the local clock to the IEEE 1588 master clock. The subsecond counter is incremented by the number passed to EMACTimestampConfigSet() in the ui32SubSecondInc parameter each time a 32-bit accumulator register generates a carry. The accumulator register is incremented by the "addend" value on each main oscillator tick, and this addend value is modified to allow fine control over the rate of change of the timestamp counter. The addend value is calculated using the ratio of the main oscillator clock rate and the desired IEEE 1588 clock rate and the ui32SubSecondInc value is set to correspond to the desired IEEE 1588 clock rate.

As an example, using digital rollover mode and a 25-MHz main oscillator clock with a desired IEEE 1588 clock accuracy of 12.5 MHz, and having made a previous call to EMACTimestampConfigSet() with ui32SubSecondInc set to the 12.5-MHz clock period of 80 ns, the initial ui32Increment value would be set to 0x80000000 to generate a carry on every second main oscillator tick. Because the system time updates each time the accumulator overflows, small changes in the ui32Increment value can be used to very finely control the system time rate.

Definition at line 3555 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_TIMADD, EMAC_O_TIMSTCTRL, EMAC_TIMSTCTRL_ADDREGUP, and HWREG.

| uint32_t EMACTimestampConfigGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32SubSecondInc | ||

| ) |

Returns the current IEEE 1588 timestamping configuration.

| ui32Base | is the base address of the controller. |

| pui32SubSecondInc | points to storage that is written with the current subsecond increment value for the IEEE 1588 clock. |

This function may be used to retreive the current MAC timestamping configuration.

If EMAC_TS_ALL_RX_FRAMES and none of the options specifying subsets of PTP packets to timestamp are set, the MAC is configured to timestamp SYNC, Follow_Up, Delay_Req and Delay_Resp messages only.

Definition at line 3282 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_SUBSECINC, EMAC_O_TIMSTCTRL, EMAC_SUBSECINC_SSINC_M, EMAC_SUBSECINC_SSINC_S, and HWREG.

| void EMACTimestampConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint32_t | ui32SubSecondInc | ||

| ) |

Configures the Ethernet MAC's IEEE 1588 timestamping options.

| ui32Base | is the base address of the controller. |

| ui32Config | contains flags selecting particular configuration options. |

| ui32SubSecondInc | is the number that the IEEE 1588 subsecond clock should increment on each tick. |

This function is used to configure the operation of the Ethernet MAC's internal timestamping clock. This clock is used to timestamp incoming and outgoing packets and as an accurate system time reference when IEEE 1588 Precision Time Protocol is in use.

The ui32Config parameter contains a collection of flags selecting the desired options. Valid flags are:

One of the following to determine whether IEEE 1588 version 1 or version 2 packet format is to be processed:

One of the following to determine how the IEEE 1588 clock's subsecond value should be interpreted and handled:

One of the following to enable or disable MAC address filtering. When enabled, PTP frames are filtered unless the destination MAC address matches any of the currently programmed MAC addresses.

One of the following to determine how the clock is updated:

One of the following to determine which IEEE 1588 messages are timestamped:

Optional, additional flags are:

The ui32SubSecondInc controls the rate at which the timestamp clock's subsecond count increments. Its meaning depends on which of EMAC_TS_DIGITAL_ROLLOVER or EMAC_TS_BINARY_ROLLOVER and EMAC_TS_UPDATE_FINE or EMAC_TS_UPDATE_COARSE were included in ui32Config.

The timestamp second counter is incremented each time the subsecond counter rolls over. In digital rollover mode, the subsecond counter acts as a simple 31-bit counter, rolling over to 0 after reaching 0x7FFFFFFF. In this case, each lsb of the subsecond counter represents 0.465 ns (assuming the definition of 1 second resolution for the seconds counter). When binary rollover mode is selected, the subsecond counter acts as a nanosecond counter and rolls over to 0 after reaching 999,999,999 making each lsb represent 1 nanosecond.

In coarse update mode, the timestamp subsecond counter is incremented by ui32SubSecondInc on each main oscillator clock tick. Setting ui32SubSecondInc to the main oscillator clock period in either 1 ns or 0.465 ns units ensures that the time stamp, read as seconds and subseconds, increments at the same rate as the main oscillator clock. For example, if the main oscillator is 25 MHz, ui32SubSecondInc is set to 40 if digital rollover mode is selected or (40 / 0.465) = 86 in binary rollover mode.

In fine update mode, the subsecond increment value must be set according to the desired accuracy of the recovered IEEE 1588 clock which must be lower than the system clock rate. Fine update mode is typically used when synchronizing the local clock to the IEEE 1588 master clock. The subsecond counter is incremented by ui32SubSecondInc counts each time a 32-bit accumulator register generates a carry. The accumulator register is incremented by the addend value on each main oscillator tick and this addend value is modified to allow fine control over the rate of change of the timestamp counter. The addend value is calculated using the ratio of the main oscillator clock rate and the desired IEEE 1588 clock rate and the ui32SubSecondInc value is set to correspond to the desired IEEE 1588 clock rate. As an example, using digital rollover mode and a 25-MHz main oscillator clock with a desired IEEE 1588 clock accuracy of 12.5 MHz, we would set ui32SubSecondInc to the 12.5-MHz clock period of 80 ns and set the initial addend value to 0x80000000 to generate a carry on every second system clock.

Definition at line 3190 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_CC_PTPCEN, EMAC_O_CC, EMAC_O_SUBSECINC, EMAC_O_TIMSTCTRL, EMAC_SUBSECINC_SSINC_M, EMAC_SUBSECINC_SSINC_S, and HWREG.

| void EMACTimestampDisable | ( | uint32_t | ui32Base | ) |

Disables packet timestamping and stops the system clock.

| ui32Base | is the base address of the controller. |

This function is used to stop the system clock used to timestamp Ethernet frames and to disable timestamping.

Definition at line 3351 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_TIMSTCTRL, EMAC_TIMSTCTRL_TSEN, and HWREG.

| void EMACTimestampEnable | ( | uint32_t | ui32Base | ) |

Enables packet timestamping and starts the system clock running.

| ui32Base | is the base address of the controller. |

This function is used to enable the system clock used to timestamp Ethernet frames and to enable that timestamping.

Definition at line 3315 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_TIMSTCTRL, EMAC_TIMSTCTRL_TSEN, EMAC_TIMSTCTRL_TSINIT, and HWREG.

| uint32_t EMACTimestampIntStatus | ( | uint32_t | ui32Base | ) |

Reads the status of the Ethernet system time interrupt.

| ui32Base | is the base address of the controller. |

When an Ethernet interrupt occurs and EMAC_INT_TIMESTAMP is reported bu EMACIntStatus(), this function must be called to read and clear the timer interrupt status.

Definition at line 3713 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_TIMSTAT, and HWREG.

| void EMACTimestampPPSCommand | ( | uint32_t | ui32Base, |

| uint8_t | ui8Cmd | ||

| ) |

Sends a command to control the PPS output from the Ethernet MAC.

| ui32Base | is the base address of the controller. |

| ui8Cmd | identifies the command to be sent. |

This function may be used to send a command to the MAC PPS (Pulse Per Second) controller when it is operating in command mode. Command mode is selected by calling EMACTimestampPPSCommandModeSet(). Valid commands are as follow:

In all cases, the width of the pulses generated is governed by the ui32Width parameter passed to EMACTimestampPPSPeriodSet(). If a command starts a train of pulses, the period of the pulses is governed by the ui32Period parameter passed to the same function. Target times associated with PPS commands are set by calling EMACTimestampTargetSet().

Definition at line 3919 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PPSCTRL, EMAC_PPSCTRL_PPSCTRL_M, EMAC_PPSCTRL_PPSEN0, and HWREG.

| void EMACTimestampPPSCommandModeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the Ethernet MAC PPS output in command mode.

| ui32Base | is the base address of the controller. |

| ui32Config | determines how the system target time is used. |

The simple mode of operation offered by the PPS (Pulse Per Second) engine may be too restrictive for some applications. The second mode, however, allows complex pulse trains to be generated using commands that tell the engine to send individual pulses or start and stop trains if pulses. In this mode, the pulse width and period may be set arbitrarily based on ticks of the clock used to update the system time. Commands are triggered at specific times using the target time last set using a call to EMACTimestampTargetSet().

The ui32Config parameter may be used to control whether the target time is used to trigger commands only or can also generate an interrupt to the CPU. Valid values are:

To use command mode, an application must call this function to enable the mode, then call:

Definition at line 3854 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PPSCTRL, EMAC_PPS_TARGET_BOTH, EMAC_PPS_TARGET_INT, EMAC_PPS_TARGET_PPS, EMAC_PPSCTRL_PPSCTRL_M, EMAC_PPSCTRL_PPSEN0, and HWREG.

| void EMACTimestampPPSPeriodSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Period, | ||

| uint32_t | ui32Width | ||

| ) |

Sets the period and width of the pulses on the Ethernet MAC PPS output.

| ui32Base | is the base address of the controller. |

| ui32Period | is the period of the PPS output expressed in terms of system time update ticks. |

| ui32Width | is the width of the high portion of the PPS output expressed in terms of system time update ticks. |

This function may be used to control the period and duty cycle of the signal output on the Ethernet MAC PPS pin when the PPS generator is operating in command mode and a command to send one or more pulses has been executed. Command mode is selected by calling EMACTimestampPPSCommandModeSet().

In simple mode, the PPS output signal frequency is controlled by the ui32FreqConfig parameter passed to EMACTimestampPPSSimpleModeSet().

The ui32Period and ui32Width parameters are expressed in terms of system time update ticks. When the system time is operating in coarse update mode, each tick is equivalent to the system clock. In fine update mode, a tick occurs every time the 32-bit system time accumulator overflows and this, in turn, is determined by the value passed to the function EMACTimestampAddendSet(). Regardless of the tick source, each tick increments the actual system time, queried using EMACTimestampSysTimeGet() by the subsecond increment value passed in the ui32SubSecondInc to EMACTimestampConfigSet().

Definition at line 3975 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PPS0INTVL, EMAC_O_PPS0WIDTH, and HWREG.

| void EMACTimestampPPSSimpleModeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32FreqConfig | ||

| ) |

Configures the Ethernet MAC PPS output in simple mode.

| ui32Base | is the base address of the controller. |

| ui32FreqConfig | determines the frequency of the output generated on the PPS pin. |

This function configures the Ethernet MAC PPS (Pulse Per Second) engine to operate in its simple mode which allows the generation of a few, fixed frequencies and pulse widths on the PPS pin. If more complex pulse train generation is required, the MAC also provides a command-based PPS control mode that can be selected by calling EMACTimestampPPSCommandModeSet().

The ui32FreqConfig parameter may take one of the following values:

Except when EMAC_PPS_SINGLE_PULSE is specified, the signal generated on PPS has a duty cycle of 50% when binary rollover mode is used for the system time subsecond count. In digital mode, the output frequency averages the value requested and is resynchronized each second. For example, if EMAC_PPS_4HZ is selected in digital rollover mode, the output generates three clocks with 50 percent duty cycle and 268 ms period followed by a fourth clock of 195 ms period, 134 ms low and 61 ms high.

Definition at line 3771 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_PPSCTRL, EMAC_O_TIMSTCTRL, EMAC_PPS_1HZ, EMAC_PPS_32768HZ, EMAC_PPS_SINGLE_PULSE, EMAC_TS_DIGITAL_ROLLOVER, and HWREG.

| void EMACTimestampSysTimeGet | ( | uint32_t | ui32Base, |

| uint32_t * | pui32Seconds, | ||

| uint32_t * | pui32SubSeconds | ||

| ) |

Gets the current system time.

| ui32Base | is the base address of the controller. |

| pui32Seconds | points to storage for the current seconds value. |

| pui32SubSeconds | points to storage for the current subseconds value. |

This function may be used to get the current system time.

The meaning of ui32SubSeconds depends on the current system time configuration. If EMACTimestampConfigSet() was previously called with the EMAC_TS_DIGITAL_ROLLOVER configuration option, each bit in the ui32SubSeconds value represents 1 ns. If EMAC_TS_BINARY_ROLLOVER was specified instead, a ui32SubSeconds bit represents 0.46 ns.

Definition at line 3437 of file emac.c.

References ASSERT, EMAC0_BASE, EMAC_O_TIMNANO, EMAC_O_TIMSEC, and HWREG.

| void EMACTimestampSysTimeSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Seconds, | ||

| uint32_t | ui32SubSeconds | ||

| ) |

Sets the current system time.

| ui32Base | is the base address of the controller. |

| ui32Seconds | is the seconds value of the new system clock setting. |

| ui32SubSeconds | is the subseconds value of the new system clock setting. |

This function may be used to set the current system time. The system clock is set to the value passed in the ui32Seconds and ui32SubSeconds parameters.

The meaning of ui32SubSeconds depends on the current system time configuration. If EMACTimestampConfigSet() was previously called with the EMAC_TS_DIGITAL_ROLLOVER configuration option, each bit in the ui32SubSeconds value represents 1 ns. If EMAC_TS_BINARY_ROLLOVER was specified instead, a ui32SubSeconds bit represents 0.46 ns.

Definition at line 3387 of file emac.c.