|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

|

EE445M RTOS

Taken at the University of Texas Spring 2015

|

Data Structures | |

| struct | tLCDIDDTiming |

| struct | tLCDRasterTiming |

Functions | |

| uint32_t | LCDModeSet (uint32_t ui32Base, uint8_t ui8Mode, uint32_t ui32PixClk, uint32_t ui32SysClk) |

| void | LCDClockReset (uint32_t ui32Base, uint32_t ui32Clocks) |

| void | LCDIDDConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | LCDIDDTimingSet (uint32_t ui32Base, uint32_t ui32CS, const tLCDIDDTiming *pTiming) |

| void | LCDIDDDMADisable (uint32_t ui32Base) |

| void | LCDIDDCommandWrite (uint32_t ui32Base, uint32_t ui32CS, uint16_t ui16Cmd) |

| void | LCDIDDDataWrite (uint32_t ui32Base, uint32_t ui32CS, uint16_t ui16Data) |

| void | LCDIDDIndexedWrite (uint32_t ui32Base, uint32_t ui32CS, uint16_t ui16Addr, uint16_t ui16Data) |

| uint16_t | LCDIDDStatusRead (uint32_t ui32Base, uint32_t ui32CS) |

| uint16_t | LCDIDDDataRead (uint32_t ui32Base, uint32_t ui32CS) |

| uint16_t | LCDIDDIndexedRead (uint32_t ui32Base, uint32_t ui32CS, uint16_t ui16Addr) |

| void | LCDIDDDMAWrite (uint32_t ui32Base, uint32_t ui32CS, const uint32_t *pui32Data, uint32_t ui32Count) |

| void | LCDRasterConfigSet (uint32_t ui32Base, uint32_t ui32Config, uint8_t ui8PalLoadDelay) |

| void | LCDRasterTimingSet (uint32_t ui32Base, const tLCDRasterTiming *pTiming) |

| void | LCDRasterACBiasIntCountSet (uint32_t ui32Base, uint8_t ui8Count) |

| void | LCDRasterEnable (uint32_t ui32Base) |

| bool | LCDRasterEnabled (uint32_t ui32Base) |

| void | LCDRasterDisable (uint32_t ui32Base) |

| void | LCDRasterSubPanelConfigSet (uint32_t ui32Base, uint32_t ui32Flags, uint32_t ui32BottomLines, uint32_t ui32DefaultPixel) |

| void | LCDRasterSubPanelEnable (uint32_t ui32Base) |

| void | LCDRasterSubPanelDisable (uint32_t ui32Base) |

| void | LCDDMAConfigSet (uint32_t ui32Base, uint32_t ui32Config) |

| void | LCDRasterPaletteSet (uint32_t ui32Base, uint32_t ui32Type, uint32_t *pui32Addr, const uint32_t *pui32SrcColors, uint32_t ui32Start, uint32_t ui32Count) |

| void | LCDRasterFrameBufferSet (uint32_t ui32Base, uint8_t ui8Buffer, uint32_t *pui32Addr, uint32_t ui32NumBytes) |

| void | LCDIntEnable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | LCDIntDisable (uint32_t ui32Base, uint32_t ui32IntFlags) |

| uint32_t | LCDIntStatus (uint32_t ui32Base, bool bMasked) |

| void | LCDIntClear (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | LCDIntRegister (uint32_t ui32Base, void(*pfnHandler)(void)) |

| void | LCDIntUnregister (uint32_t ui32Base) |

| #define CYCLES_FROM_TIME_NS | ( | ui32ClockFreq, | |

| ui32Time_nS | |||

| ) |

This macro can be used to convert from time in nanoseconds to periods of the supplied clock in Hertz as required when setting up the LIDD and raster timing structures. The calculation will round such that the number of cycles returned represents no longer a time than specified in the ui32Time_nS parameter. Values of ui32Time_nS less than or equal to 35791394 (35.79 milliseconds) are supported by the macro. Larger values will cause arithmetic overflow and yield incorrect values. It is further assumed that ui32ClockFreq is a non-zero multiple of 1000000 (1MHz).

| #define CYCLES_FROM_TIME_US | ( | ui32ClockFreq, | |

| ui32Time_uS | |||

| ) |

This macro can be used to convert from time in microseconds to periods of the supplied clock in Hertz as required when setting up the LIDD and raster timing structures. The calculation will round such that the number of cycles returned represents no longer a time than specified in the ui32Time_uS parameter. Values of ui32Time_uS less than or equal to 4294967uS (4.29 seconds) are supported by the macro. Larger values will cause arithmetic overflow and yield incorrect values. It is further assumed that ui32ClockFreq is a non-zero multiple of 1000000 (1MHz).

| #define LCD_CLOCK_CORE 0x00000001 |

Definition at line 408 of file lcd.h.

Referenced by LCDClockReset().

| #define LCD_CLOCK_DMA 0x00000004 |

Definition at line 406 of file lcd.h.

Referenced by LCDClockReset().

| #define LCD_CLOCK_LIDD 0x00000002 |

Definition at line 407 of file lcd.h.

Referenced by LCDClockReset().

| #define LCD_CLOCK_MAIN 0x00000008 |

Definition at line 405 of file lcd.h.

Referenced by LCDClockReset(), and LCDRasterEnable().

| #define LCD_INT_AC_BIAS_CNT 0x00000008 |

Definition at line 353 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_DMA_DONE 0x00000001 |

Definition at line 349 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_EOF0 0x00000100 |

Definition at line 356 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_EOF1 0x00000200 |

Definition at line 357 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_PAL_LOAD 0x00000040 |

Definition at line 355 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_RASTER_FRAME_DONE 0x00000002 |

Definition at line 350 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_SYNC_LOST 0x00000004 |

Definition at line 352 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_INT_UNDERFLOW 0x00000020 |

Definition at line 354 of file lcd.h.

Referenced by LCDIntClear(), LCDIntDisable(), and LCDIntEnable().

| #define LCD_MODE_AUTO_UFLOW_RESTART ((uint8_t)0x02) |

Definition at line 282 of file lcd.h.

Referenced by LCDModeSet().

| #define LCD_MODE_LIDD ((uint8_t)0x00) |

Definition at line 280 of file lcd.h.

Referenced by LCDModeSet().

| #define LCD_MODE_RASTER ((uint8_t)0x01) |

Definition at line 281 of file lcd.h.

Referenced by LCDModeSet().

| #define LCD_PALETTE_SRC_24BIT 0x80000000 |

Definition at line 398 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_PALETTE_TYPE_1BPP 0x00000000 |

Definition at line 393 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_PALETTE_TYPE_2BPP 0x00001000 |

Definition at line 394 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_PALETTE_TYPE_4BPP 0x00002000 |

Definition at line 395 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_PALETTE_TYPE_8BPP 0x00003000 |

Definition at line 396 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_PALETTE_TYPE_DIRECT 0x00004000 |

Definition at line 397 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define LCD_SUBPANEL_AT_BOTTOM 0x00000000 |

Definition at line 416 of file lcd.h.

Referenced by LCDRasterSubPanelConfigSet().

| #define LCD_SUBPANEL_AT_TOP 0x20000000 |

Definition at line 415 of file lcd.h.

Referenced by LCDRasterSubPanelConfigSet().

| #define LIDD_CONFIG_ASYNC_HITACHI 0x00000004 |

Definition at line 294 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_ASYNC_MPU68 0x00000001 |

Definition at line 291 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_ASYNC_MPU80 0x00000003 |

Definition at line 293 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_INVERT_ALE 0x00000008 |

Definition at line 296 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_INVERT_CS0 0x00000040 |

Definition at line 301 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_INVERT_CS1 0x00000080 |

Definition at line 302 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_INVERT_RS_EN 0x00000010 |

Definition at line 297 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_INVERT_WS_DIR 0x00000020 |

Definition at line 299 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_SYNC_MPU68 0x00000000 |

Definition at line 290 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define LIDD_CONFIG_SYNC_MPU80 0x00000002 |

Definition at line 292 of file lcd.h.

Referenced by LCDIDDConfigSet().

| #define PAL_FROM_RGB | ( | ui32RGBColor | ) |

This macro can be used to convert a 24-bit RGB color value as used by the TivaWare Graphics Library into a 12-bit LCD controller color palette entry.

Definition at line 68 of file lcd.h.

Referenced by LCDRasterPaletteSet().

| #define RASTER_ACTVID_DURING_BLANK 0x08000000 |

Definition at line 332 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_ACTIVE_24BPP_PACKED 0x02000080 |

Definition at line 314 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_ACTIVE_24BPP_UNPACKED 0x06000080 |

Definition at line 316 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_ACTIVE_PALETTIZED_12BIT 0x00000080 |

Definition at line 318 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_ACTIVE_PALETTIZED_16BIT 0x00800080 |

Definition at line 320 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_PASSIVE_COLOR_12BIT 0x00000000 |

Definition at line 328 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_PASSIVE_COLOR_16BIT 0x01000000 |

Definition at line 330 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_PASSIVE_MONO_4PIX 0x00000002 |

Definition at line 322 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_PASSIVE_MONO_8PIX 0x00000202 |

Definition at line 324 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_FMT_PASSIVE_PALETTIZED 0x00000000 |

Definition at line 326 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_LOAD_DATA_ONLY 0x00200000 |

Definition at line 336 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_LOAD_PALETTE_ONLY 0x00100000 |

Definition at line 337 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_NIBBLE_MODE_ENABLED 0x00400000 |

Definition at line 334 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_READ_ORDER_REVERSED 0x00000100 |

Definition at line 339 of file lcd.h.

Referenced by LCDRasterConfigSet().

| #define RASTER_TIMING_ACTIVE_LOW_HSYNC 0x00200000 |

Definition at line 188 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_ACTIVE_LOW_OE 0x00800000 |

Definition at line 180 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_ACTIVE_LOW_PIXCLK 0x00400000 |

Definition at line 184 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_ACTIVE_LOW_VSYNC 0x00100000 |

Definition at line 192 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_SYNCS_ON_FALLING_PIXCLK 0x03000000 |

Definition at line 176 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_SYNCS_ON_RISING_PIXCLK 0x02000000 |

Definition at line 174 of file lcd.h.

Referenced by LCDRasterTimingSet().

| #define RASTER_TIMING_SYNCS_OPPOSITE_PIXCLK 0x00000000 |

Definition at line 172 of file lcd.h.

Referenced by LCDRasterTimingSet().

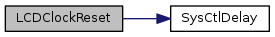

| void LCDClockReset | ( | uint32_t | ui32Base, |

| uint32_t | ui32Clocks | ||

| ) |

Resets one or more of the LCD controller clock domains.

| ui32Base | specifies the LCD controller module base address. |

| ui32Clocks | defines the subset of clock domains to be reset. |

This function allows sub-modules of the LCD controller to be reset under software control. The ui32Clocks parameter is the logical OR of the following clocks:

In all cases, LCD controller register values are preserved across these resets.

Definition at line 181 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_CLOCK_CORE, LCD_CLOCK_DMA, LCD_CLOCK_LIDD, LCD_CLOCK_MAIN, and SysCtlDelay().

Referenced by LCDRasterEnable().

| void LCDDMAConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Configures the LCD controller's internal DMA engine.

| ui32Base | is the base address of the controller. |

| ui32Config | provides flags defining the desired DMA parameters. |

This function is used to configure the DMA engine within the LCD controller. This engine is responsible for performing bulk data transfers to the display when in LIDD mode or for transferring palette and pixel data from SRAM to the display panel when in raster mode.

The ui32Config parameter is a logical OR of various flags. It must contain one value from each of the following groups.

The first group of flags set the number of words that have to be in the FIFO before it signals that it is ready:

The second group of flags set the number of 32-bit words in each DMA burst transfer:

The final group of flags set internal byte lane controls and allow byte swapping within the DMA engine. The label represents the output byte order for an input 32-bit word ordered ``0123''.

Additionally, LCD_DMA_PING_PONG may be specified. This flag configures the controller to operate in double-buffered mode. When data is scanned out from the first frame buffer, the DMA engine immediately moves to the second frame buffer and scans from there before moving back to the first. If this flag is clear, the DMA engine uses a single frame buffer, restarting the scan from the beginning of the buffer each time it completes a frame.

Definition at line 1293 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_DMACTL_BIGDEND, LCD_DMACTL_BURSTSZ_M, LCD_DMACTL_BYTESWAP, LCD_DMACTL_FIFORDY_M, LCD_DMACTL_FMODE, and LCD_O_DMACTL.

| void LCDIDDCommandWrite | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint16_t | ui16Cmd | ||

| ) |

Writes a command to the display when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

| ui16Cmd | is the 16-bit command word to write. |

This function writes a 16-bit command word to the display when the LCD controller is in LIDD mode. A command write occurs with the ALE signal active.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 401 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0ADDR, and LCD_O_LIDDCS1ADDR.

| void LCDIDDConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config | ||

| ) |

Sets the LCD controller communication parameters when in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32Config | defines the display interface configuration. |

This function is used when the LCD controller is configured in LIDD mode and specifies the configuration of the interface between the controller and the display panel. The ui32Config parameter is comprised of one of the following modes:

Additional flags may be ORed into ui32Config to control the polarities of various control signals:

Definition at line 258 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCTL, LIDD_CONFIG_ASYNC_HITACHI, LIDD_CONFIG_ASYNC_MPU68, LIDD_CONFIG_ASYNC_MPU80, LIDD_CONFIG_INVERT_ALE, LIDD_CONFIG_INVERT_CS0, LIDD_CONFIG_INVERT_CS1, LIDD_CONFIG_INVERT_RS_EN, LIDD_CONFIG_INVERT_WS_DIR, LIDD_CONFIG_SYNC_MPU68, and LIDD_CONFIG_SYNC_MPU80.

| uint16_t LCDIDDDataRead | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS | ||

| ) |

Reads a data word from the display when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

This function reads the 16-bit data word from the display when the LCD controller is in LIDD mode. A data read occurs with the ALE signal inactive.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 603 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0DATA, and LCD_O_LIDDCS1DATA.

| void LCDIDDDataWrite | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint16_t | ui16Data | ||

| ) |

Writes a data value to the display when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

| ui16Data | is the 16-bit data word to write. |

This function writes a 16-bit data word to the display when the LCD controller is in LIDD mode. A data write occurs with the ALE signal inactive.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 446 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0DATA, and LCD_O_LIDDCS1DATA.

| void LCDIDDDMADisable | ( | uint32_t | ui32Base | ) |

Disables internal DMA operation when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

When the LCD controller is operating in LCD Interface Display Driver mode, this function must be called after completion of a DMA transaction and before calling LCDIDDCommandWrite(), LCDIDDDataWrite(), LCDIDDStatusRead(), LCDIDDIndexedWrite(), LCDIDDIndexedRead() or LCDIDDDataRead() to disable DMA mode and allow CPU-initiated transactions to the display.

Definition at line 364 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_LIDDCTL_DMAEN, and LCD_O_LIDDCTL.

| void LCDIDDDMAWrite | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| const uint32_t * | pui32Data, | ||

| uint32_t | ui32Count | ||

| ) |

Writes a block of data to the display using DMA when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

| pui32Data | is the address of the first 16-bit word to write. This address must be aligned on a 32-bit word boundary. |

| ui32Count | is the number of 16-bit words to write. This value must be a multiple of 2. |

This function writes a block of 16-bit data words to the display using DMA. It is only valid when the LCD controller is in LIDD mode. Completion of the DMA transfer is signaled by the LCD_INT_DMA_DONE interrupt.

This function enables DMA mode prior to starting the transfer. The caller is responsible for ensuring that any earlier DMA transfer has completed before initiating another transfer.

During the time that DMA is enabled, none of the other LCD LIDD data transfer functions may be called. When the DMA transfer is complete and the application wishes to use the CPU to communicate with the display, LCDIDDDMADisable() must be called to disable DMA access prior to calling LCDIDDCommandWrite(), LCDIDDDataWrite(), LCDIDDStatusRead(), LCDIDDIndexedWrite(), LCDIDDIndexedRead() or LCDIDDDataRead().

Definition at line 721 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_LIDDCTL_DMACS, LCD_LIDDCTL_DMAEN, LCD_O_DMABAFB0, LCD_O_DMACAFB0, and LCD_O_LIDDCTL.

| uint16_t LCDIDDIndexedRead | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint16_t | ui16Addr | ||

| ) |

Reads a given display register when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

| ui16Addr | is the address of the display register to read. |

This function reads a 16-bit word from a register in the display when the LCD controller is in LIDD mode and configured to use either the Motorola (LIDD_CONFIG_SYNC_MPU68 or LIDD_CONFIG_ASYNC_MPU68) or Intel (LIDD_CONFIG_SYNC_MPU80 or LIDD_CONFIG_ASYNC_MPU80) modes that employ an external address latch.

When configured in Hitachi mode (LIDD_CONFIG_ASYNC_HITACHI), this function should not be used. In this case, the functions LCDIDDStatusRead() and LCDIDDDataRead() may be used to read status and data bytes from the panel.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 655 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0ADDR, LCD_O_LIDDCS0DATA, LCD_O_LIDDCS1ADDR, and LCD_O_LIDDCS1DATA.

| void LCDIDDIndexedWrite | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| uint16_t | ui16Addr, | ||

| uint16_t | ui16Data | ||

| ) |

Writes data to a given display register when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

| ui16Addr | is the address of the display register to write. |

| ui16Data | is the data to write. |

This function writes a 16-bit data word to a register in the display when the LCD controller is in LIDD mode and configured to use either the Motorola (LIDD_CONFIG_SYNC_MPU68 or LIDD_CONFIG_ASYNC_MPU68) or Intel (LIDD_CONFIG_SYNC_MPU80 or LIDD_CONFIG_ASYNC_MPU80) modes that employ an external address latch.

When configured in Hitachi mode (LIDD_CONFIG_ASYNC_HITACHI), this function should not be used. In this case the functions LCDIDDCommandWrite() and LCDIDDDataWrite() may be used to transfer command and data bytes to the panel.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 500 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0ADDR, LCD_O_LIDDCS0DATA, LCD_O_LIDDCS1ADDR, and LCD_O_LIDDCS1DATA.

| uint16_t LCDIDDStatusRead | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS | ||

| ) |

Reads a status word from the display when the LCD controller is in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select to use. Valid values are 0 and 1. |

This function reads the 16-bit status word from the display when the LCD controller is in LIDD mode. A status read occurs with the ALE signal active. If the interface is configured in Hitachi mode (LIDD_CONFIG_ASYNC_HITACHI), this operation corresponds to a command mode read.

This function must not be called if the LIDD interface is currently configured to expect DMA transactions. If DMA was previously used to write to the panel, LCDIDDDMADisable() must be called before this function can be used.

Definition at line 558 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_LIDDCS0ADDR, and LCD_O_LIDDCS1ADDR.

| void LCDIDDTimingSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32CS, | ||

| const tLCDIDDTiming * | pTiming | ||

| ) |

Sets the LCD controller interface timing when in LIDD mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32CS | specifies the chip select whose timings are to be set. |

| pTiming | points to a structure containing the desired timing parameters. |

This function is used in LIDD mode to set the setup, strobe and hold times for the various interface control signals. Independent timings are stored for each of the two supported chip selects offered by the LCD controller.

For a definition of the timing parameters required, see the definition of tLCDIDDTiming.

Definition at line 301 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_LIDDCS0CFG_GAP_S, LCD_LIDDCS0CFG_RDDUR_S, LCD_LIDDCS0CFG_RDHOLD_S, LCD_LIDDCS0CFG_RDSU_S, LCD_LIDDCS0CFG_WRDUR_S, LCD_LIDDCS0CFG_WRHOLD_S, LCD_LIDDCS0CFG_WRSU_S, LCD_O_LIDDCS0CFG, LCD_O_LIDDCS1CFG, tLCDIDDTiming::ui8DelayCycles, tLCDIDDTiming::ui8RSDuration, tLCDIDDTiming::ui8RSHold, tLCDIDDTiming::ui8RSSetup, tLCDIDDTiming::ui8WSDuration, tLCDIDDTiming::ui8WSHold, and tLCDIDDTiming::ui8WSSetup.

| void LCDIntClear | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Clears LCD controller interrupt sources.

| ui32Base | is the base address of the controller. |

| ui32IntFlags | is a bit mask of the interrupt sources to be cleared. |

The specified LCD controller interrupt sources are cleared so that they no longer assert. This function must be called in the interrupt handler to keep the interrupt from being triggered again immediately upon exit.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1709 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_INT_AC_BIAS_CNT, LCD_INT_DMA_DONE, LCD_INT_EOF0, LCD_INT_EOF1, LCD_INT_PAL_LOAD, LCD_INT_RASTER_FRAME_DONE, LCD_INT_SYNC_LOST, LCD_INT_UNDERFLOW, and LCD_O_MISCLR.

| void LCDIntDisable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Disables individual LCD controller interrupt sources.

| ui32Base | is the base address of the controller. |

| ui32IntFlags | is the bit mask of the interrupt sources to be disabled. |

This function disables the indicated LCD controller interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1594 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_INT_AC_BIAS_CNT, LCD_INT_DMA_DONE, LCD_INT_EOF0, LCD_INT_EOF1, LCD_INT_PAL_LOAD, LCD_INT_RASTER_FRAME_DONE, LCD_INT_SYNC_LOST, LCD_INT_UNDERFLOW, and LCD_O_IENC.

| void LCDIntEnable | ( | uint32_t | ui32Base, |

| uint32_t | ui32IntFlags | ||

| ) |

Enables individual LCD controller interrupt sources.

| ui32Base | is the base address of the controller. |

| ui32IntFlags | is the bit mask of the interrupt sources to be enabled. |

This function enables the indicated LCD controller interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

The ui32IntFlags parameter is the logical OR of any of the following:

Definition at line 1544 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_INT_AC_BIAS_CNT, LCD_INT_DMA_DONE, LCD_INT_EOF0, LCD_INT_EOF1, LCD_INT_PAL_LOAD, LCD_INT_RASTER_FRAME_DONE, LCD_INT_SYNC_LOST, LCD_INT_UNDERFLOW, and LCD_O_IM.

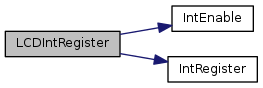

| void LCDIntRegister | ( | uint32_t | ui32Base, |

| void(*)(void) | pfnHandler | ||

| ) |

Registers an interrupt handler for the LCD controller module.

| ui32Base | specifies the LCD controller module base address. |

| pfnHandler | is a pointer to the function to be called when the LCD controller interrupt occurs. |

This function registers the handler to be called when the LCD controller module interrupt occurs.

Definition at line 1744 of file lcd.c.

References ASSERT, INT_LCD0_TM4C129, IntEnable(), IntRegister(), and LCD0_BASE.

| uint32_t LCDIntStatus | ( | uint32_t | ui32Base, |

| bool | bMasked | ||

| ) |

Gets the current LCD controller interrupt status.

| ui32Base | is the base address of the controller. |

| bMasked | is false if the raw interrupt status is required and true if the masked interrupt status is required. |

This function returns the interrupt status for the LCD controller. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

Definition at line 1643 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_MISCLR, and LCD_O_RISSET.

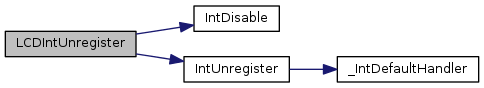

| void LCDIntUnregister | ( | uint32_t | ui32Base | ) |

Unregisters the interrupt handler for the LCD controller module.

| ui32Base | specifies the LCD controller module base address. |

This function unregisters the interrupt handler and disables the global LCD controller interrupt in the interrupt controller.

Definition at line 1782 of file lcd.c.

References ASSERT, INT_LCD0_TM4C129, IntDisable(), IntUnregister(), and LCD0_BASE.

| uint32_t LCDModeSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8Mode, | ||

| uint32_t | ui32PixClk, | ||

| uint32_t | ui32SysClk | ||

| ) |

Configures the basic operating mode and clock rate for the LCD controller.

| ui32Base | specifies the LCD controller module base address. |

| ui8Mode | specifies the basic operating mode to be used. |

| ui32PixClk | specifies the desired LCD controller pixel or master clock rate in Hz. |

| ui32SysClk | specifies the current system clock rate in Hz. |

This function sets the basic operating mode of the LCD controller and also its master clock. The ui8Mode parameter may be set to either LCD_MODE_LIDD or LCD_MODE_RASTER. LCD_MODE_LIDD is used to select LCD Interface Display Driver mode for character panels connected via an asynchronous interface (CS, WE, OE, ALE, data) and LCD_MODE_RASTER is used to communicate with panels via a synchronous video interface using data and sync signals. Additionally, LCD_MODE_AUTO_UFLOW_RESTART may be ORed with either of these modes to indicate that the hardware should restart automatically if a data underflow occurs.

The ui32PixClk parameter specifies the desired master clock for the the LCD controller. In LIDD mode, this value controls the MCLK used in communication with the display and valid values are between ui32SysClk and ui32SysClk/255. In raster mode, ui32PixClk specifies the pixel clock rate for the raster interface and valid values are between ui32SysClk/2 and ui32SysClk/255. The actual clock rate set may differ slightly from the desired rate due to the fact that only integer dividers are supported. The rate set will, however, be no higher than the requested value.

The ui32SysClk parameter provides the current system clock rate and is used to allow the LCD controller clock rate divisor to be correctly set to give the desired ui32PixClk rate.

Definition at line 110 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_CLKEN_CORE, LCD_CLKEN_DMA, LCD_CLKEN_LIDD, LCD_CTL_CLKDIV_S, LCD_MODE_AUTO_UFLOW_RESTART, LCD_MODE_LIDD, LCD_MODE_RASTER, LCD_O_CLKEN, and LCD_O_CTL.

| void LCDRasterACBiasIntCountSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8Count | ||

| ) |

Sets the number of AC bias pin transitions per interrupt.

| ui32Base | is the base address of the controller. |

| ui8Count | is the number of AC bias pin transitions to count before the AC bias count interrupt is asserted. Valid values are from 0 to 15. |

This function is used to set the number of AC bias transitions between each AC bias count interrupt (LCD_INT_AC_BIAS_CNT). If ui8Count is 0, no AC bias count interrupt is generated.

Definition at line 974 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRTIM2, LCD_RASTRTIM2_ACBI_M, and LCD_RASTRTIM2_ACBI_S.

| void LCDRasterConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Config, | ||

| uint8_t | ui8PalLoadDelay | ||

| ) |

Sets the LCD controller interface timing when in raster mode.

| ui32Base | specifies the LCD controller module base address. |

| ui32Config | specifies properties of the raster interface and the attached display panel. |

| ui8PalLoadDelay | specifies the number of system clocks to wait between each 16 halfword (16-bit) burst when loading the palette from SRAM into the internal palette RAM of the controller. |

This function configures the basic operating mode of the raster interface and specifies the type of panel that the controller is to drive.

The ui32Config parameter must be defined as one of the following to select the required target panel type and output pixel format:

Additionally, the following flags may be ORed into ui32Config:

If the LCD controller's raster engine is enabled when this function is called, it is disabled as a result of the call.

Definition at line 846 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRCTL, LCD_RASTRCTL_REQDLY_S, RASTER_ACTVID_DURING_BLANK, RASTER_FMT_ACTIVE_24BPP_PACKED, RASTER_FMT_ACTIVE_24BPP_UNPACKED, RASTER_FMT_ACTIVE_PALETTIZED_12BIT, RASTER_FMT_ACTIVE_PALETTIZED_16BIT, RASTER_FMT_PASSIVE_COLOR_12BIT, RASTER_FMT_PASSIVE_COLOR_16BIT, RASTER_FMT_PASSIVE_MONO_4PIX, RASTER_FMT_PASSIVE_MONO_8PIX, RASTER_FMT_PASSIVE_PALETTIZED, RASTER_LOAD_DATA_ONLY, RASTER_LOAD_PALETTE_ONLY, RASTER_NIBBLE_MODE_ENABLED, and RASTER_READ_ORDER_REVERSED.

| void LCDRasterDisable | ( | uint32_t | ui32Base | ) |

Disables the raster output.

| ui32Base | is the base address of the controller. |

This function disables the LCD controller raster output and stops driving the attached display.

Definition at line 1079 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRCTL, and LCD_RASTRCTL_LCDEN.

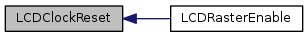

| void LCDRasterEnable | ( | uint32_t | ui32Base | ) |

Enables the raster output.

| ui32Base | is the base address of the controller. |

This function enables the LCD controller raster output and starts displaying the content of the current frame buffer on the attached panel. Prior to enabling the raster output, LCDModeSet(), LCDRasterConfigSet(), LCDDMAConfigSet(), LCDRasterTimingSet(), LCDRasterPaletteSet() and LCDRasterFrameBufferSet() must have been called.

Definition at line 1014 of file lcd.c.

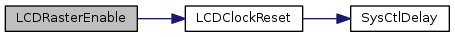

References ASSERT, HWREG, LCD0_BASE, LCD_CLOCK_MAIN, LCD_O_RASTRCTL, LCD_RASTRCTL_LCDEN, and LCDClockReset().

| bool LCDRasterEnabled | ( | uint32_t | ui32Base | ) |

Determines whether or not the raster output is currently enabled.

| ui32Base | is the base address of the controller. |

This function may be used to query whether or not the raster output is currently enabled.

Definition at line 1047 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRCTL, and LCD_RASTRCTL_LCDEN.

| void LCDRasterFrameBufferSet | ( | uint32_t | ui32Base, |

| uint8_t | ui8Buffer, | ||

| uint32_t * | pui32Addr, | ||

| uint32_t | ui32NumBytes | ||

| ) |

Sets the LCD controller frame buffer start address and size in raster mode.

| ui32Base | is the base address of the controller. |

| ui8Buffer | specifies which frame buffer to configure. Valid values are 0 and 1. |

| pui32Addr | points to the first byte of the frame buffer. This pointer must be aligned on a 32-bit (word) boundary. |

| ui32NumBytes | specifies the size of the frame buffer in bytes. This value must be a multiple of 4. |

This function is used to configure the position and size of one of the two supported frame buffers while in raster mode. The second frame buffer (configured when ui8Buffer is set to 1) is only used if the controller is set to operate in ping-pong mode (by specifying the LCD_DMA_PING_PONG configuration flag on a call to LCDDMAConfigSet()).

The format of the frame buffer depends on the image type in use and the current raster configuration settings. If RASTER_LOAD_DATA_ONLY was specified in a previous call to LCDRasterConfigSet(), the frame buffer contains only packed pixel data in the required bit depth and format. In other cases, the frame buffer comprises a palette of either 8 or 128 32-bit words followed by the packed pixel data. The palette size is 8 words (16 16-bit entries) for all pixel formats other than 8bpp which uses a palette of 128 words (256 16-bit entries). Note that the 8 word palette is still present even for 12, 16 and 24-bit formats, which do not use the lookup table.

The frame buffer size, specified using the ui32NumBytes parameter, must be the palette size (if any) plus the size of the image bitmap required for the currently configured display resolution.

ui32NumBytes = (Palette Size) + ((Width * Height) * BPP) / 8)

If RASTER_LOAD_DATA_ONLY is not specified, frame buffers passed to this function must be initialized using a call to LCDRasterPaletteSet() prior to enabling the raster output. If this is not done, the pixel format identifier and color table required by the hardware is not present and the results are unpredictable.

Definition at line 1476 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_DMABAFB0, LCD_O_DMABAFB1, LCD_O_DMACAFB0, and LCD_O_DMACAFB1.

| void LCDRasterPaletteSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Type, | ||

| uint32_t * | pui32Addr, | ||

| const uint32_t * | pui32SrcColors, | ||

| uint32_t | ui32Start, | ||

| uint32_t | ui32Count | ||

| ) |

Initializes the color palette in a frame buffer.

| ui32Base | is the base address of the controller. |

| ui32Type | specifies the type of pixel data to be held in the frame buffer and also the format of the source color values passed. |

| pui32Addr | points to the start of the frame buffer into which the palette information is to be written. |

| pui32SrcColors | points to the first color value that is to be written into the frame buffer palette. |

| ui32Start | specifies the index of the first color in the palette to update. |

| ui32Count | specifies the number of source colors to be copied into the frame buffer palette. |

This function is used to initialize the color palette stored at the beginning of a frame buffer. It writes the relevant pixel type into the first entry of the frame buffer and copies the requested number of colors from a source buffer into the palette starting at the required index, optionally converting them from 24-bit color format into the 12-bit format used by the LCD controller.

ui32Type must be set to one of the following values to indicate the type of frame buffer for which the palette is being initialized:

Optionally, the LCD_PALETTE_SRC_24BIT flag may be ORed into ui32Type to indicate that the supplied colors in the pui32SrcColors array are in the 24-bit format as used by the TivaWare Graphics Library with one color stored in each 32-bit word. In this case, the colors read from the source array are converted to the 12-bit format used by the LCD controller before being written into the frame buffer palette.

If LCD_PALETTE_SRC_24BIT is not present, it is assumed that the pui32SrcColors array contains 12-bit colors in the format required by the LCD controller with 2 colors stored in each 32-bit word. In this case, the values are copied directly into the frame buffer palette without any reformatting.

Definition at line 1367 of file lcd.c.

References ASSERT, LCD0_BASE, LCD_PALETTE_SRC_24BIT, LCD_PALETTE_TYPE_1BPP, LCD_PALETTE_TYPE_2BPP, LCD_PALETTE_TYPE_4BPP, LCD_PALETTE_TYPE_8BPP, LCD_PALETTE_TYPE_DIRECT, and PAL_FROM_RGB.

| void LCDRasterSubPanelConfigSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32Flags, | ||

| uint32_t | ui32BottomLines, | ||

| uint32_t | ui32DefaultPixel | ||

| ) |

Sets the position and size of the subpanel on the raster display.

| ui32Base | is the base address of the controller. |

| ui32Flags | may be either LCD_SUBPANEL_AT_TOP to show frame buffer image data in the top portion of the display and default color in the bottom portion, or LCD_SUBPANEL_AT_BOTTOM to show image data at the bottom of the display and default color at the top. |

| ui32BottomLines | defines the number of lines comprising the bottom portion of the display. If LCD_SUBPANEL_AT_TOP is set in ui32Flags, these lines contain the default pixel color when the subpanel is enabled, otherwise they contain image data. |

| ui32DefaultPixel | is the 24-bit RGB color to show in the portion of the display not configured to show image data. |

The LCD controller provides a feature that allows a portion of the display to be filled with a default color rather than image data from the frame buffer. This feature reduces SRAM bandwidth requirements because no data is fetched for lines containing the default color. This feature is only available when the LCD controller is in raster mode and configured to drive an active matrix display.

The subpanel area containing image data from the frame buffer may be positioned either at the top or bottom of the display as controlled by the value of ui32Flags. The height of the bottom portion of the display is defined by ui32BottomLines.

When a subpanel is configured, the application must also reconfigure the frame buffer to ensure that it contains the correct number of lines for the subpanel size in use. This configuration can be achieved by calling LCDRasterFrameBufferSet() with the ui32NumBytes parameter set appropriately to describe the required number of active video lines in the subpanel area.

The subpanel display mode is not enabled using this function. To enable the subpanel once it has been configured, call LCDRasterSubPanelEnable().

Definition at line 1134 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRSUBP1, LCD_O_RASTRSUBP2, LCD_RASTRSUBP1_DPDLSB_S, LCD_RASTRSUBP1_LPPT_M, LCD_RASTRSUBP1_LPPT_S, LCD_RASTRSUBP1_SPEN, LCD_RASTRSUBP2_DPDMSB_M, LCD_SUBPANEL_AT_BOTTOM, and LCD_SUBPANEL_AT_TOP.

| void LCDRasterSubPanelDisable | ( | uint32_t | ui32Base | ) |

Disables subpanel display mode.

| ui32Base | is the base address of the controller. |

This function disables subpanel display mode and reverts to showing the entire frame buffer image on the display. After the subpanel is disabled, the frame buffer size must be reconfigured to match the full dimensions of the display area by calling LCDRasterFrameBufferSet() with an appropriate value for the ui32NumBytes parameter.

Definition at line 1219 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRSUBP1, and LCD_RASTRSUBP1_SPEN.

| void LCDRasterSubPanelEnable | ( | uint32_t | ui32Base | ) |

Enables subpanel display mode.

| ui32Base | is the base address of the controller. |

This function enables subpanel display mode and displays a default color rather than image data in the number of lines and at the position specified by a previous call to LCDRasterSubPanelConfigSet(). Prior to calling LCDRasterSubPanelEnable(), the frame buffer should have been reconfigured to match the desired subpanel size using a call to LCDRasterFrameBufferSet().

Subpanel display is only possible when the LCD controller is in raster mode and is configured to drive an active matrix display.

Definition at line 1190 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRSUBP1, and LCD_RASTRSUBP1_SPEN.

| void LCDRasterTimingSet | ( | uint32_t | ui32Base, |

| const tLCDRasterTiming * | pTiming | ||

| ) |

Sets the LCD controller interface timing when in raster mode.

| ui32Base | specifies the LCD controller module base address. |

| pTiming | points to a structure containing the desired timing parameters. |

This function is used in raster mode to set the panel size and sync timing parameters.

For a definition of the timing parameters required, see the definition of tLCDRasterTiming.

Definition at line 894 of file lcd.c.

References ASSERT, HWREG, LCD0_BASE, LCD_O_RASTRTIM0, LCD_O_RASTRTIM1, LCD_O_RASTRTIM2, LCD_RASTRTIM0_HBP_S, LCD_RASTRTIM0_HFP_S, LCD_RASTRTIM0_HSW_S, LCD_RASTRTIM0_MSBPPL_S, LCD_RASTRTIM0_PPL_S, LCD_RASTRTIM1_LPP_S, LCD_RASTRTIM1_VBP_S, LCD_RASTRTIM1_VFP_S, LCD_RASTRTIM1_VSW_S, LCD_RASTRTIM2_ACBF_S, LCD_RASTRTIM2_ACBI_M, LCD_RASTRTIM2_HSW_S, LCD_RASTRTIM2_MSBHBP_S, LCD_RASTRTIM2_MSBHFP_S, LCD_RASTRTIM2_MSBLPP_S, RASTER_TIMING_ACTIVE_LOW_HSYNC, RASTER_TIMING_ACTIVE_LOW_OE, RASTER_TIMING_ACTIVE_LOW_PIXCLK, RASTER_TIMING_ACTIVE_LOW_VSYNC, RASTER_TIMING_SYNCS_ON_FALLING_PIXCLK, RASTER_TIMING_SYNCS_ON_RISING_PIXCLK, RASTER_TIMING_SYNCS_OPPOSITE_PIXCLK, tLCDRasterTiming::ui16HBackPorch, tLCDRasterTiming::ui16HFrontPorch, tLCDRasterTiming::ui16HSyncWidth, tLCDRasterTiming::ui16PanelHeight, tLCDRasterTiming::ui16PanelWidth, tLCDRasterTiming::ui32Flags, tLCDRasterTiming::ui8ACBiasLineCount, tLCDRasterTiming::ui8VBackPorch, tLCDRasterTiming::ui8VFrontPorch, and tLCDRasterTiming::ui8VSyncWidth.